## Signal Integrity Verification for On-Chip Long Interconnect Lines

Victor Avendaño

May 7, 2005

## Sumario

Los circuitos integrados (CIs) que son fabricados con tecnologías actuales presentan estructuras complejas. CIs actuales pueden contener una gran cantidad de sistemas. Estos sistemas trabajando en conjunto logran realizar la función o funciones para que fue diseñado el CI. El CI con estas características es llamado SoC (por sus siglas en inglés). Estos tipos de circuitos son el resultado de la gran capacidad de integración que permiten las tecnologías actuales. Varios millones de transistores pueden ser agrupados dentro de un CI. Esto aumenta considerablemente la densidad de líneas de interconexión necesarias dentro del CI.

Las líneas de interconexión pueden transportar señales con frecuencias en el rango de los gigahertz. La alta densidad de estas líneas de interconexión y señales viajando a altas frequencias hacen que el acoplamiento entre líneas tengan un impacto importante en la integridad de la señal que viaje por las líneas de interconexón.

Es importante conocer los problemas de integridad que pueden presentar las señales que viajan dentro del chip. Esto permitirá establecer técnicas de verficación que ayuden a saber cuando una señal no tiene los niveles adecuados de integridad.

La tesis esta organizada de la siguiente manera:

El Capítulo 1 da una introducción al estado del arte del diseño electrónico actual y los problemas que se surgen al utilizar tecnologías nanométricas. Algunos trabajos relacionados con la verificación de integridad de señal son presentados.

El capitulo 2 presenta un análisis the la integridad de la señal en líneas

de interconexion. El caso de implementar líneas de protección en un bus de datos para reducir los efectos de acoplamiento capacitivos e inductivos es presentado y analizado. En este capítulo se presenta una metodología para analizar el impacto de las líneas de protección en la integridad de la señal cuando estas presentan un defecto.

El Capítulo 3 presenta una nueva metodología de verificación de integridad de señal. Dos monitores son utilizados para detectar violaciones de integridad de la señal en los estados lógicos alto y bajo de una señal digital. Es posible mediante esta metodología verificar más de dos señales con solo dos monitores.

El Capítulo 4 muestra los resultados experimentales obtenidos mediante las mediciones realizadas al circuito integrado diseñado y fabricado. Diversas mediciones son realizadas para mostrar el buen funcionamiento de la metodologia propuesta.

En el Capítulo 5 se presentan las conclusiones de la tesis.

## Acknowledgments

#### Al Consejo Nacional de Ciencia y Tecnología (CONACYT)

Por el soporte económico brindado y las facilidades otorgadas

## Al Instituto Nacional de Astrofísica, Óptica y Electrónica

Por darme la oportunidad de realizar mi carrera profesional

#### Al Dr. Victor Champac Vilela

Por su paciencia, dedicacion y apoyo personal al trabajo realizado.

#### Al Dr. Joan Figueras

Por todo el apoyo brindado durante mi estancia en Barcelona.

A los Doctores:

Edmundo Gutiérrez Domínguez Mónico Linares Aranda Antonio Zenteno Ramírez José Ernesto Rayas Sánchez Andre Ivanov

Por la revisión y cometarios sobre la tesis.

## **Dedicates**

Quiero dedicar esta tesis esta a :

#### Rita y Viquito

a quienes amo y han sido mi soporte y estímulo para mi desarrollo profesional y personal. Gracias por soportar las ausencias y los momentos difíciles.

#### A mis padres

#### **Blanca y Victor**

que con su amor y apoyo me han guiado siempre en los momentos difíciles. A mis hermanas

#### Rosario, Olivia y Olga

que en todo momento me han dado su apoyo incondicional. A todos mis familiares que siempre me han demostrado su cariño A Doña Rosa, Don Daniel, Conchita, Arturo, Daniel y Gloria por demostrar siempre su cariño.

Quiero agradecer de manera especial a todos mis compañeros y amigos por su apoyo y sus consejos y una disculpa anticipada si olvido a alguien: Rene, Julio, Abenamar, Carlos M, Victor-J, Arturo, Aldrin, Oscar, Omar, Manuel, Nestor, Andres, Rogelio, Adan, Felipe, Guilebaldo, Antonio, Luis, Fernando. A los amigos que me brindaron su hospitalidad y apoyo en Barcelona: Alberto, Carmen, Betín, Miguel, Mónica, Juan K, Nelly, John-Jairo, Jousep-Rius, Rosa, Salvador, Xavi.

A Claudia, Nacho, Rocio, Netza por el apoyo técnico brindado.

A las chicas de la coordinacion docente: Rocio, Aremi, Esther, Ceci, Lupita, Landy y bety. Y a todos los seres que han puesto los elementos para que se culmine este trabajo.

## Contents

| Sı | ımar  | io                                                   | i    |

|----|-------|------------------------------------------------------|------|

| A  | ckno  | wledgments                                           | iii  |

| D  | edica | ites                                                 | V    |

| Pı | efac  | е                                                    | хi   |

| A  | crony | /ms                                                  | xiii |

| 1  | Intr  | oduction                                             | 1    |

|    | 1.1   | Performance of actual electronic systems             | 3    |

|    | 1.2   | Testing of high performance circuits                 |      |

|    | 1.3   |                                                      | 9    |

|    | 1.4   | Related signal integrity verification techniques     | 12   |

|    | 1.5   | Organization of the thesis                           | 14   |

| 2  | Inte  | erconnect characterization and signal integrity loss | 17   |

|    | 2.1   | Coupling between interconnects                       | 18   |

|    | 2.2   | Simple interconnect models                           | 20   |

|    |       | 2.2.1 One stage model                                | 21   |

|    |       | 2.2.2 Two stage model                                | 23   |

|    |       | 2.2.3 Three stage model                              | 23   |

|    | 2.3   | Shielding practice                                   | 26   |

|    | 2.4   | Characterization of signal quality                   |      |

|    | 2.5   | S-Plane signal integrity regions                     | 34   |

|    | 2.6   | Conclusions                                          | 34   |

viii CONTENTS

| 3 | Veri  |         | n of signal integrity using High Speed Monitors       | 39  |

|---|-------|---------|-------------------------------------------------------|-----|

|   | 3.1   |         | luction                                               | 40  |

|   | 3.2   |         | sed Verification Methodology                          | 41  |

|   | 3.3   | Propos  | sed sensors                                           | 44  |

|   |       | 3.3.1   | High level SIV Monitor                                | 45  |

|   |       | 3.3.2   | Low level SIV Monitor                                 | 46  |

|   |       | 3.3.3   | Multi-signal Monitors                                 | 48  |

|   |       | 3.3.4   | Monitor Performance                                   | 50  |

|   | 3.4   | Cohere  | ent sampling                                          | 55  |

|   |       | 3.4.1   | 1 0                                                   | 58  |

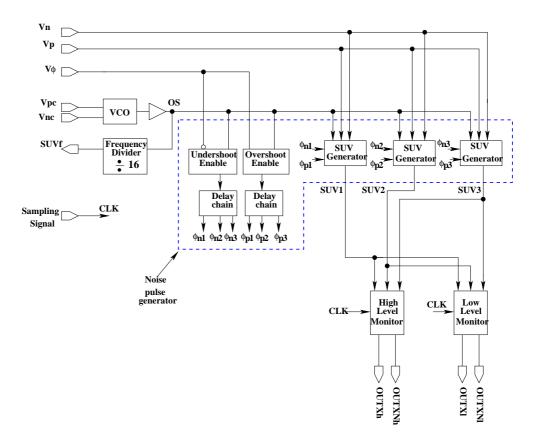

|   | 3.5   | Monite  | oring system architecture                             | 61  |

|   |       | 3.5.1   | Monitor Selector                                      | 62  |

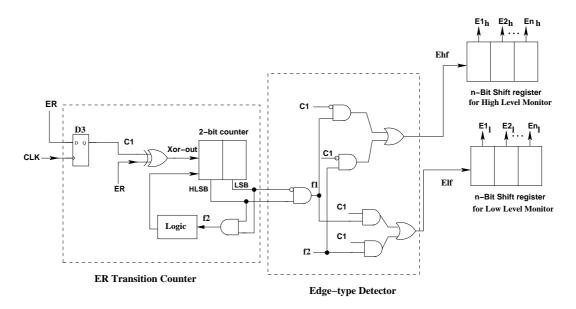

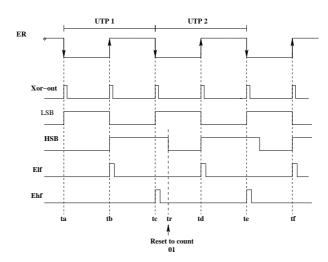

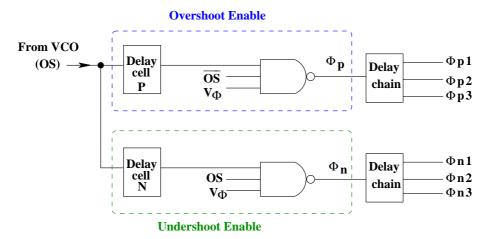

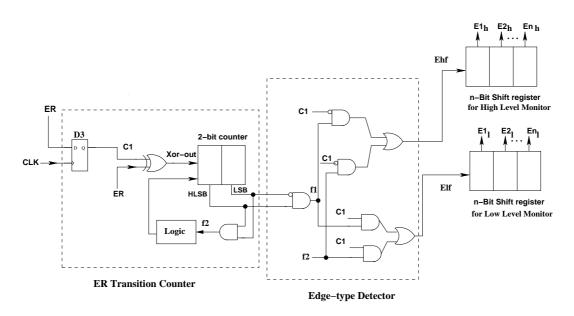

|   |       | 3.5.2   | Enable signal generator                               | 64  |

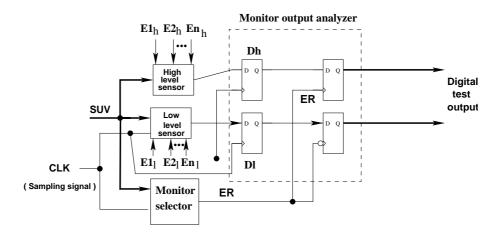

|   |       | 3.5.3   | Monitor output analyzer                               | 70  |

|   | 3.6   | Metho   | odology accuracy                                      | 71  |

|   |       | 3.6.1   | Cost of the proposed verification methodology         | 76  |

|   | 3.7   | Conclu  | usions                                                | 78  |

| 4 | Silie | con Val | lidation                                              | 81  |

|   | 4.1   | Circui  | ts designed                                           | 82  |

|   |       | 4.1.1   |                                                       |     |

|   |       | 4.1.2   | Module with controlled frequency of the SUV           |     |

|   |       | 4.1.3   | Module with fixed high frequency of the SUV           | 99  |

|   | 4.2   | Measu   | rements for the high level monitors                   | 101 |

|   |       | 4.2.1   | Measurements in DC                                    |     |

|   |       | 4.2.2   | Measurements for the module with controlled frequency |     |

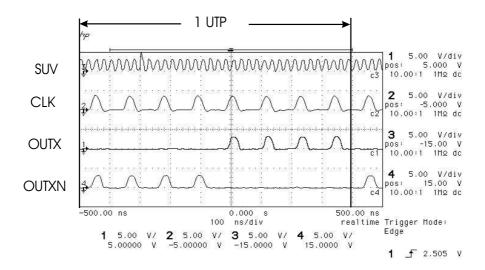

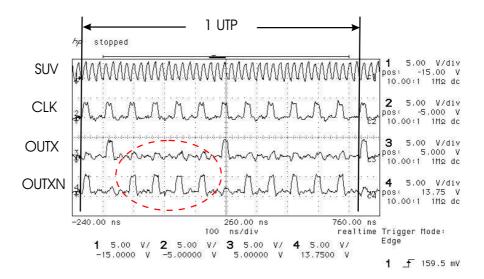

|   |       |         | of the SUV, $f_{SUV} = 640MHz$                        | 104 |

|   |       | 4.2.3   | Measurement to the module of the high frequency of    |     |

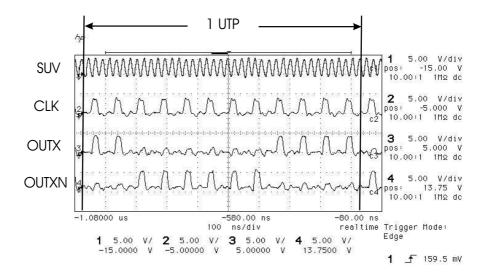

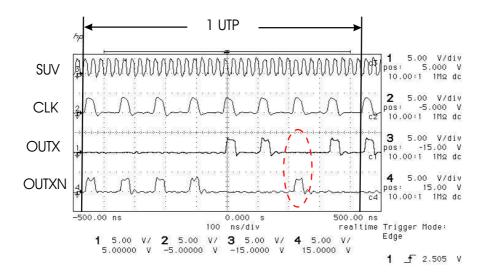

|   |       |         | the SUV, $f_{SUV} = 917MHz$                           | 112 |

|   | 4.3   | Measu   | rements for the low level monitors                    | 116 |

|   |       | 4.3.1   | Measurements in DC                                    | 117 |

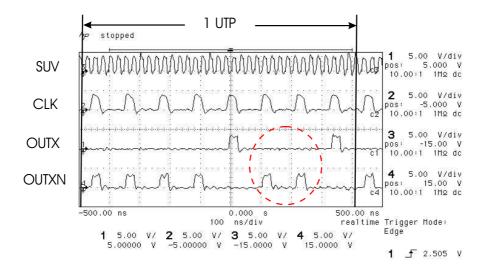

|   |       | 4.3.2   | Measurements to the module with controlled frequency  |     |

|   |       |         | of the SUV, $f_{SUV} = 640MHz$                        | 118 |

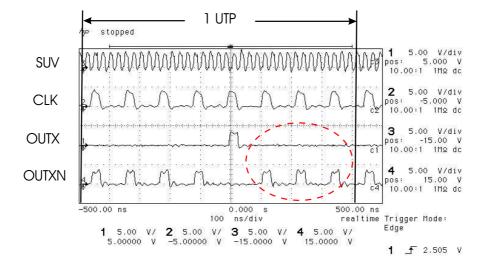

|   |       | 4.3.3   | Measurement to the module of the high frequency of    |     |

|   |       |         | the SUV, $f_{SUV} = 917MHz$                           | 124 |

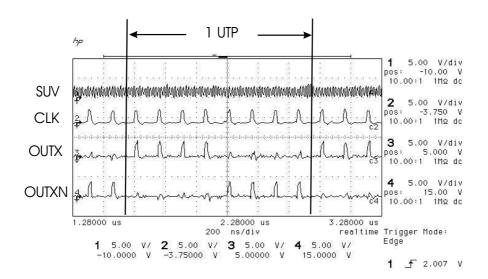

|   | 4.4   | Estima  | ation of the noise pulse width injected to the SUV    |     |

|   | 4.5   |         | usions                                                |     |

| $\mathbf{C}$ | ONTENTS                     | ix  |

|--------------|-----------------------------|-----|

| 5            | Conclusions                 | 135 |

| Α            | Two-Bit counter performance | 139 |

| Re           | esumen                      | 153 |

X CONTENTS

## **Preface**

The integrated circuits (ICs) fabricated with current technologies are complex. These ICs can implement several systems to achieve a specific function or functions. This type of ICs is called system on chip (SoC). This feature of the current ICs is due to the nanometric technologies that allows to integrate millions of transistors into a single chip. A large variety of design possibilities is given with these technologies to implement analogue and mixed-signal circuits in the same substrate.

Microprocessors, for example, can be combined with high precision digital to analogue and analogue to digital converter in the same chip. This allows to save manufacturing cost, because the chip to chip interconnections are reduced. However, the amount of implemented transistors and on-chip interconnects is increased with these nanometric technologies. Also each new scaled technology allow to increase the frequency performance of the implemented circuitry. These characteristics, the high density of on-chip interconnects, transistors and high rates of switching activity generate several new issues in current integrated circuits. An important issue is the signal integrity degradation due to capacitive and inductive coupling between interconnects, the electromagnetic effects generated at high frequencies, process variation, and manufacturing defects

A current design challenge is to assure acceptable signal integrity levels in order to have the correct performance of the overall system. Because of this, signal integrity verification is important to advise if violations of the signal integrity occur in the implemented systems. The effort of the verification techniques is addressed for solving the issues like signal skew, jitter, ringings, etc. The scope of this work is to analyze and present a methodology for signal integrity violation in interconnects, and to propose a verification technique in order to detect the unacceptable ringing in high speed digital signals. The

thesis is organized as follows:

Chapter 1 gives an introduction of the current state of the art of the electronic design and the issues generated by using nanometric technologies. Some works related to signal integrity verification are presented

Chapter 2 analyze the signal integrity in interconnects. The performance at high frequencies of these interconnects are obtained by simulation. The case of implementing shielding lines in a bus structure is also analyzed. A methodology to analyze the impact of shielding line defects over the signal integrity is proposed.

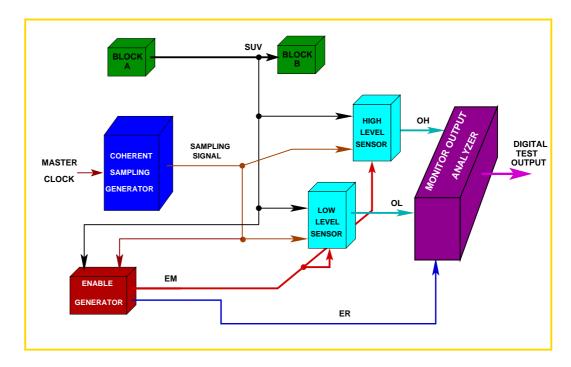

Chapter 3 proposes a novel signal integrity verification methodology. High speed signals are verified by using two monitors. Undershoots in the high logic levels and overshoots in the low logic level are sensed by the high and low level monitor respectively. The methodology uses a coherent sampling scheme to capture the signal information. A complete scheme to verify more than two signals is also presented.

Chapter 4 presents the experimental results obtained for designed and fabricated circuits. Several measurement are made in order to show the feasibility of the proposed methodology.

Chapter 5 gives the conclusion of the work. The obtained results and contribution of the thesis are presented.

## Acronyms

ADC Analog to Digital Converter

ATE Automatic Test Equipment

CAD Computer Aided Design

CDF Commulative Distribution Function

DAC Digital to Analog Converter

DFT Design For Test

FFT Fast Fourier Transform

HSB High Significant Bit

I/O Input/Output

IC Integrated Circuit

ITRS International Technology Roadmap for Semiconductors

LSB Low Significant Bit MNA Modified Nodal Analysis

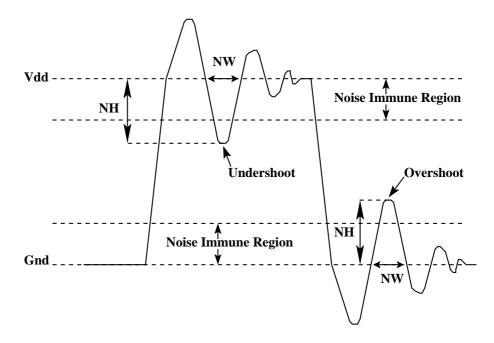

NH Noise Heigh NW Noise Width

OD Overshoot Detector

PEEC Partial Element Equivalent Circuit

PLL Phase Locked Loop RF Radio Frequency SI Signal Integrity

SIV Signal Integrity Violation

SoC System on Chip

SUV Signal Under Verification

UTP Unit Test Period

VCO Voltage Controlled Oscilator VLSI Very Large Scale Integrated

## Chapter 1

## Introduction

During the last decades the growing of the electronic industry has been based in the evolution of the semiconductor technology. Technologies have been scaled down according to the Moore law [1] [2]. This has allowed improvements in cost per function and performance. The increasing clock rate and SoC integration presents severe challenges in the design and test of current complex integrated circuits [3]. Due to this, the designer needs to prevent new problems like crosstalk noise, substrate noise, power supply drop, etc [4]. All these factors can affect the signal integrity and may produce an unreliable performance of the system. Many of these new issues appearing in modern technologies can be solved if proper testability and DFT strategies are considered and incorporated early in the design phase. However, some of these problems may remain and appear during the field application. This is because is not possible to take into account all the possible environmental and required signal combinations during the design phase. Hence, verification methodologies for identifying these problems before delivering the product to the customer are required.

Verification of signal integrity requires testers at the GHz range which are expensive. Furthermore, external speed verification is not possible for the newest technologies. Due to this built-in verification strategies appear as a good alternative for current nanometer technologies.

The first section of chapter presents the performance of current electronic systems. The characteristics, emerging issues and challenges for this actual systems are presented. The issue of testing for these systems is explained

next. Then, the signal integrity concern is presented. Next section shows the related work of signal integrity verification. Finally, the last section presents the organization of this thesis.

## 1.1 Performance of actual electronic systems

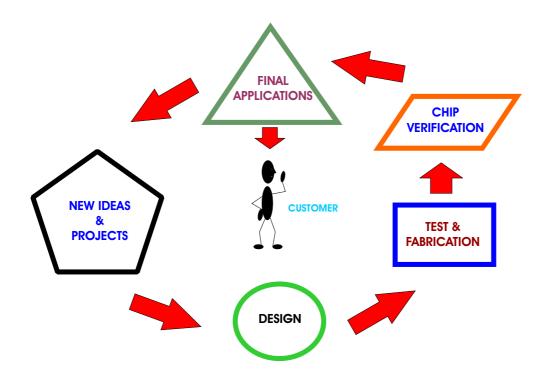

Design technology is the discipline that transforms the project ideas of the electronic designers into manufactured and testable representations [1]. Designers need several elements in order to make real their ideas. Those elements like tools, libraries, manufacturing process characteristics, and methodologies help the designer to get the conception, implementation, and validation of microelectronics-based systems. Furthermore a better understanding of the relationship between electronic science and physical science is required.

Figure 1.1: Ideas and objectives are transformed in electronic applications

For instance, the theories of electron devices and circuits components are built on principles of solid-state physics, statistical mechanics, and thermodynamics [5]. Nowadays, the traditional circuit theory is not adequate to deal with the many complex problems that have emerged since the advent of the Very Large Scale Integrated (VLSI) circuits. In VLSI systems it is found a big number of active devices and interconnects where their components interact

strongly with each other. In this case, the traditional circuit theory is unable to manipulate, in a adequately way, the analysis. In these cases, numerical analysis is effective to predict the behavior of well-specified circuits with the parameters values specified, but it provides no general understanding of the circuits. Often, interpretation of the simulation results is the hardest part of the circuit design verification. All the previously mentioned factors are important issues in current high performance integrated circuits [5] [6] [7].

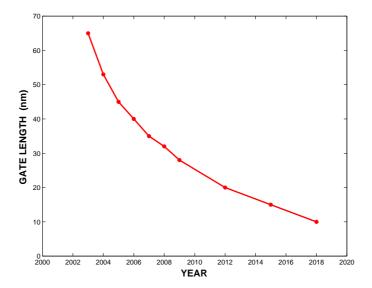

The principal actor in these current circuits is the transistor. The transistors fabricated with actual technologies have features sizes (channel widths and lengths) in the range of nanometers. Transistors with these features may turn-on or turn-off at very short times. Because this, the frequency performance of the circuits designed with these transistors can get high rates. The roadmap for feature sizes (gate length) from the year 2003 to the year 2018 is presented in Fig. 1.2 [1].

Figure 1.2: Road-map of the transistor gate length trough the years. Data taken of the ITRS 2004.

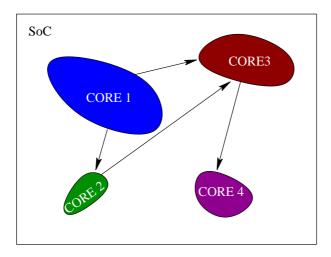

The integration capacity in current technologies allows to have millions of transistors in a single chip [8] [9]. Complete systems can be implemented

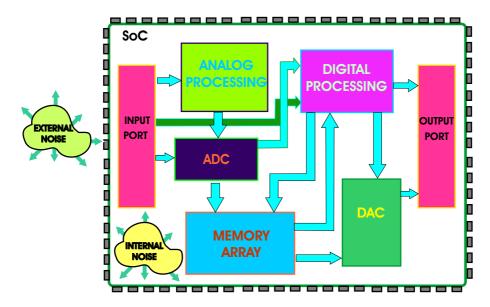

in these chips. The circuits implementing systems in a single die are called System on Chips (SoCs). In this approach, a set of circuits is used to perform a specific function or functions into of a digital or analogue core, and a set of cores into a single chip builds the so called SoCs. Fig. 1.3 shows a SoC built with several cores.

Figure 1.3: Several cores are used to make a system on chip (SoC).

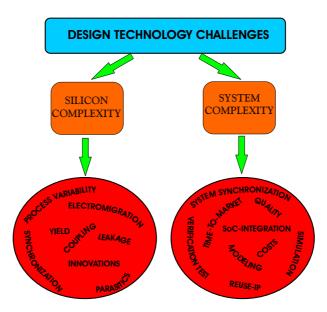

The SoC implementation and new technologies arise design complexities [1]: Silicon complexity and system complexity (see Fig. 1.4).

The first one refers to the impact of process scaling and the introduction of new materials or device and interconnect architectures. The second one refers to exponentially increasing amount of transistors in a single chip. Because silicon complexity, several previously ignored phenomena are currently becoming of quite importance in new technologies [8] [5]. As indicated by International Technology Roadmap for Semiconductors in [1], the predominant sub-micron effects are:

- non-ideal scaling of device parasitics, supply and threshold voltages,

- coupled high-frequency devices and interconnects,

- manufacturing variability

- scaling global interconnect performance relative to device performance (communication, synchronization)

Figure 1.4: Complexities and challenges for current design technologies

- decreased reliability (gate insulator tunneling and breakdown integrity, electro-migration, general fault tolerance)

- complexity of manufacturing hand-off (reticle enhancement and mask writing/inspection flow)

In system complexity, the higher integration of devices is due to the smaller features sizes and spurred by consumer demand for increased functionality, lower cost, and shorter time-to-market. Design specification and validation become extremely challenging, particularly with respect to complex operating context. Trade-off must be made between all aspects of value or quality, and all aspects of cost. Implied challenges include:

- reuse (modeling, simulation, verification, test of component blocks)

- verification and test

- design process management (design team size and geographic distribution, data management, collaborative design support, metrics and continuous process improvement)

The acknowledge of the additional considerations such as design reuse and manufactured system cost in the design optimization must be shared [5] [1]

[10]. Together, the silicon and system complexity challenges imply exponentially increasing complexity of the design process. In order to deal with this complexity, design technology must in general provide optimization and analysis of more complex objectives and constrains.

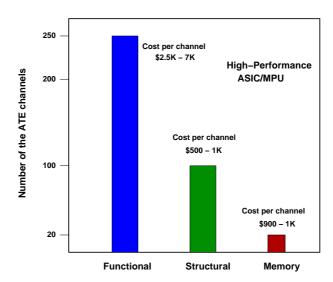

### 1.2 Testing of high performance circuits

The task to inspect the correct circuit performance falls in the test discipline [11] [12]. A lot of work to test different type of faults has been developed for many years. With the advent of the nanometric technologies, the test has increased in complexity. Nanometric technologies allow to integrate millions of logic gates in a single chip, thousand of external pins, and clock rates of the order of gigahertz. Chips with these features make difficult the task of the test. Test cost per unit and test equipment capital cost consideration continue to dominate test methodology decisions. Design for test (DFT) methodologies have contributed to reduce the cost of the test equipment [13]. However, this cost continue being significant [1] [14]. Fig. 1.5 shows, as example, the number of automatic test equipment (ATE) channels and the cost per channel for different kind of tests. This example is for ASICmicroprocessors using functional, structural and memory test. The total test cost is given by the cost per channel and the cost for the number of channels plus the base cost. The base cost include the mechanical infrastructure, black-plane, central instruments, and other resources. The base cost for the ASIC-microprocessors is in the order of \$250K - \$550K [1]. If the system complexity continues growing as expected, the ATE would require more pins to test the system, hence the test cost is also increased. Systems-on-Chip (SOC) designs are breaking the traditional barriers between digital, analog, RF, and mixed-signal test equipment capability requirements, resulting in a trend toward highly configurable, one-platform-fits-all test solution [5] [15]. A different approach is clearly needed.

Test automatization is required for the semiconductor industry in order to continue producing faster, smaller and powerful commercially viable chips. One approach to counteract these issues is given by implementing test circuits onto the chip. This means making more use of DFT techniques. The basic idea of the DFT is to identify key internal nodes and to implement the required structures to make those nodes accessible from outside the chip.

Figure 1.5: Number of the ATE channels required to accomplish three different kind of test to the ASIC microprocessors [1].

The goal for using any DFT technique is to achieve the detection of the highest number of potential faults. It means, to increase as much as possible the fault coverage. DFT-based test approaches require continue research to increase coverage of actual process defects through development of advanced and feasible test methodologies. It is expected that DFT technologies will continue to lag leading-edge device performance and complexity.

At-speed functional test has provided a robust methodology for high volume manufacturing for many years. The use of this methodology has allowed to achieve high quality levels [16] [17]. It can be argued that this method is reaching its limits for several reasons, such as test development resources, manufacturing yield loss, and cost [18] [19]. Even if there is an affordable process to upgrade or replace manufacturing test equipment as the device performance improves with each scaled technology. It has been proved to be impossible to avoid the resource requirement for manual test writing in the functional test environment. Test content generation may require tens of person years for highly complex designs [1] [20]. DFT techniques like scan and Built-in-Self Test (BIST) either enable test content to be generated automatically or reduce the test content generation effort. Hence, it reduces drastically the manual test writing task. For highly complex integrated de-

vices, DFT is required to provide re-use test collateral and avoid a geometric or exponential growth of the test development and validation effort [21] [5] [20].

An important emerging issue in nanometric technologies is signal integrity. Capacitance coupling between interconnects, large number of interconnects and gigahertz frequencies are determinant factors which affect the performance and reliability of high performance SoCs [2] [14] [8]. On-chip signal integrity verification is required in order to assure the correct performance of the entire chip [22] [23].

In the next section, the signal integrity issue is analyzed.

## 1.3 Signal integrity issue

High speed electronics operates actually in a ultra-wide frequency band up to several tens of gigahertz. At these frequencies, several electromagnetic effects can produce signal integrity degradation [24] [25] [26] [27]. Signal integrity violation (SIV) can be produced by several sources of noise. Substrate noise is an important issue because it can affect noise-sensitive circuitries such as analog blocks. When a digital block switch, current is injected toward substrate by coupling of the interconnects and devices. This substrate current may cause interference or a faulty behavior of a sensitive circuit near to the digital block. Another problem is due to large power nets and long interconnects that cause power supply drops. Current technologies permit to integrate an increasing number of devices onto a chip. The large amount of devices connected to the power supply net increases the current consumption at different points of the net. Localized drops of the  $V_{DD}$  level are difficult to predict. The performance of the system is affected by increased delay and reduction of noise margin.

Interconnects play a major role in signal integrity, hence, they significantly impact the system performance. The current and future design challenge of the SoCs are to connect efficiently the core components into a reliable network in order to perform the desired functions. Because of this, it is possible to have on-chip micro-networks [28] [29]. In general the communications between cores into the SoC may present errors due to technology factors like voltage ringings. Other factors are electromagnetic interference as well

as capacitive and inductive crosstalk. Long interconnects running close to each other present a significant coupling capacitance. This is because the lateral capacitance is quite important in actual integrated circuits [30] [31]. Furthermore, in high performance systems the inductive coupling between interconnects becomes significant and the total inductance of the interconnect should be taken into account [32].

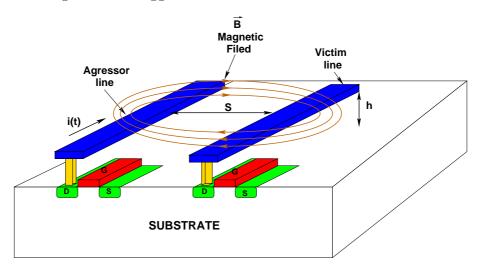

Signal current variations on an interconnect generates a variable magnetic field. This magnetic flux  $(\vec{B})$  creates an electric field  $\overline{E}$  and this  $\overline{E}$  generates, on near loops, inductive voltage noise as show in Fig. 1.6. Levels of crosstalk noise depend on the coupling capacitance/inductance between interconnects, the total resistance and capacitance of interconnect and the driver strengths of the aggressor and victim lines. The distributions of the

Figure 1.6: A changing magnetic field due to a current variation through to the interconnect cause a induced voltage in a near interconnect.

electromagnetic fields depend on the logic blocks and interconnects physical distribution. Furthermore, they also depend on the switching activity of the signals traveling across them. The integrity features of the signals traveling across interconnects have an strong dependence on the switching activity of the input signals.

Because current technologies allow to integrate more and more coupled interconnects, the higher switching speeds of the signals cause many integrity problems. The dependency of the signal integrity characteristics on the switching activity is needed to be taken into account for the signal integrity verification of the circuit performance [33] [23]. In coupled lines, the signal propagation delay could vary 50% of the propagation delay of a single isolated line with the same physical structure [33].

The coupling influence in critical signals is addressed by inserting shields between interconnects. These shields are additional  $V_{DD}$  and GND wires which typically are inserted between critical global interconnects. The capacitive coupling is almost eliminated by the shield wire. Also the self-inductance of the wire is reduced by the shield wire because the electric field return path around the interconnect is provided very close to the line. The shield wire also limits the inductive coupling between interconnects on either side of the shield wire by reducing the electric field [33][34].

With a great number of critical interconnects switching at very fast frequencies, the number of the shielding wires is increased in order to reduce the capacitive and inductive coupling. The effective capacitance and inductance of the interconnect is determined by the switching activity and not only by the physical features. The shielding wires can be switched in order to reduce the return path of the electric field (loop inductance) and the delay by the capacitive coupling [35] [36]. The recommended ratio between the signal and shield wire is 2:1 for the design of high performance processors [37] [27]. The connections of the shielding lines to ground could present resistive open defects [38]. A resistive open appears when the conductive material is not completely broken. This defect indirectly affects the integrity of the signal traveling on adjacent signal lines. Ringing values of the signal could vary significantly. Hence, a faulty behavior of the system can occur [35] [34].

Characteristics of interconnects as narrow width, closeness of the wiring, etc., affect directly the SI [30] [34]. To ensure SI, designers need to consider circuit design, placement and routing, and circuit simulation. Current tools could help the designer in all these tasks. A good approach in order to minimize noise level is to be careful and methodical in circuit simulation [6]. The problem is that all possible environmental and signal combinations are unlikely to be taken into account in the simulation. Consequently practical experience shows SI violations not foreseen by the present state of the art CAD tools. Verification of critical signals would require testers at GHz range

which are expensive. Furthermore, external at-speed verification may not be possible for newest technologies. Due to this built-in verification appears as a good alternative. This strategy also allows to verify some internal nodes difficult to control or to observe at the I/O pins.

In the next section, several related works to signal integrity verification are shown.

## 1.4 Related signal integrity verification techniques

As explained before, signal integrity is an important issue in actual high performance circuits. Also the interconnect effects play an important role in the signal integrity verification (SIV) of high speed signals. Several studies for interconnect impact on circuit performance can be found in [34] [39] [32] [33] [37] [2]. Several crosstalk defect-oriented analysis solutions have been developed on multiple-coupled interconnects. The work presented in [40] shows a crosstalk-defect simulation methodology. This approach allows a fast analysis for interconnects dominated by capacitive coupling and estimate the noise effects based in the interconnect signal transitions. Other analysis about the crosstalk and their impact in signal integrity can be found in [41] [23] [42] [43].

Problems such as skew and jitter are present in actual SoCs structures where sets of long interconnects are present. Some studies of these problems can be found in [44] [45] [21]. The authors in [46] present a test pattern generation algorithm for signal integrity faults on long interconnects. In this approach it is possible to detect intermittent failures due to integrity loss on long interconnects.

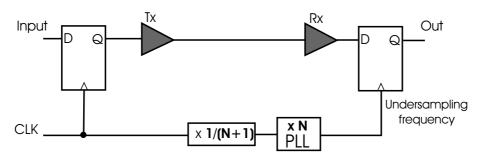

In [47] the authors presents a sense amplifier for detecting small delay variation between two signals. In [48] the authors present on-chip mechanisms including testing of interconnects for signal integrity by extending the JTAG standard, but they did not include the effect of mutual inductance and their sensor is noise-sensitive. Another important contribution is given in [49] where cells to detect noise and skew are presented. However, one sensor per cell is required to verify each critical signal, which penalizes the area. In the approach presented in [50], the authors propose a frequency-based

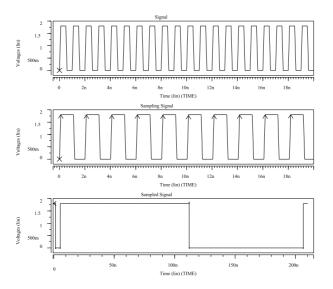

technique for measurement jitter. They analyze sampled data at low frequency and shift the data into a tester using software-based analysis. This technique coherently under-sample a received signal by clocking the receiver at a frequency slightly lower (beat frequency) than the transmitted data frequency (see Fig. 1.7). The output of the latch is a synchronous data

Figure 1.7: Jitter measurement technique using coherent under-sampling.

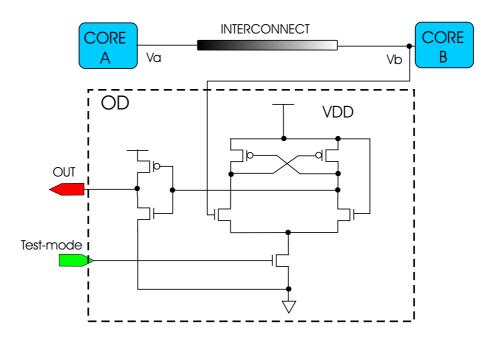

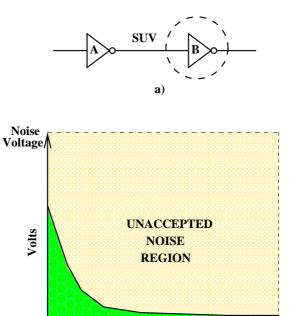

stream that can be descrialized and analyzed on-chip at low frequency using software-based analysis. The technique focus on the unstable bits in the output caused by rising/falling-edge jitter to measure the statistical properties of the jitter. By having groups of these unstable bits the authors derive a cumulative distribution function (CDF) and from these CDF they derive a jitter histogram. The drawback of this approach is that the technique need to generate an under-sampling frequency just slightly lower than the system high speed clock, this is still a high frequency signal for clock speeds at rates of gigahertz. An interesting work about testing overshoots can be found in [51]. The authors present a CMOS overshoot detector (OD) cell, which consists of a modified cross-coupled PMOS differential sense amplifier for detecting voltage overshoots in bus lines. Fig. 1.8 shows the detector cell.

Their OD cell sits physically near the receiving core and observe the actual signal plus noise received by core B (see Fig. 1.8). The output stored in the OD cell is analyzed by a DFT decision. Three choices to transfer the information to the output are presented. One of them is by using a compressor to compact the information given by the OD cell. Then the information can be sent-out through scan registers. Another way is recording the occurrence of overshoots in flip-flops. The information is also scanned-out. The last option given by authors is using a counter for collecting information of overshoots occurrence. The outputs of the OD cells are connected to a n-input

Figure 1.8: Overshoots testing: A CMOS cross-coupled sense amplifier.

NAND gate, which output will be **1** if at least one overshoot occurs (the output of the OD cell is **0** if a overshoot occurs). The output of the NAND gate is connected to the clock line of a counter to record the number of times that the core input is exposed to overshoots. This proposal is efficient for testing the occurrence of voltage value above  $V_{DD}$  (overshoots) in a bus system, but it is not able to sense ringing or undershoots.

## 1.5 Organization of the thesis

The rest of the document is organized as follows: The chapter 2 shows the interconnect modeling and an approach to establish the integrity features of the interconnect for several lengths. The performance at high frequencies of interconnects are obtained by simulation. The impact of shielding lines to reduce the crosstalk in a bus structure is also analyzed. A methodology to analyze the effects of shielding line defects over the signal integrity is proposed.

A novel signal integrity verification methodology is proposed in chapter 3. Digital signals are verified by using two monitors. Undershoots in the high logic levels and overshoots in the low logic level are sensed by the high and low level monitor respectively. The methodology uses a coherent sampling scheme to capture the signal information. A complete scheme to verify more than two signals is also presented. A control circuitry to verify several signals under the sampling scheme is proposed

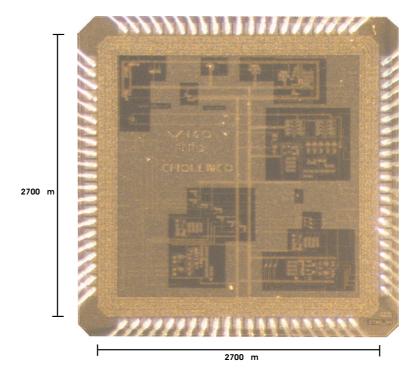

Chapter 4 presents the experimental results obtained measuring the performance of the designed and fabricated signal integrity monitors. Also, the coherent sampling scheme applied with the proposed monitors has been validated.

Finally, the conclusions of the thesis are given in chapter 5. The contributions of the thesis work are discussed in this chapter. Also, the constraints and future work are presented in this chapter.

## Chapter 2

# Interconnect characterization and signal integrity loss

Interconnect structures in high speed circuits play an important role in present and future CMOS technologies. Inductance and capacitance coupling effects (crosstalk) may cause significant loss in signal integrity in high performance systems. One way to reduce these effects is to place a signal line between two grounded lines (shield). The shielding lines are connected to ground from the metal wire to the substrate through vias. In this chapter we study the influence of defective grounding of shielding lines. We focus on resistive open defects due to manufacturing problems or broken vias. Faulty shields may cause undershoots or ringings in signal traveling in long interconnect lines. An analysis of the interconnect behavior in the presence of a resistive open has been performed using a lumped RLC circuit in one, two, three stages and compared with the interconnect Hspice model. Simple expressions for undershoots and overshoots have been derived using dominant poles to determine the zones of signal integrity violation for different lengths of interconnect lines. The results show the impact of defective grounded shields.

The chapter is organized as follows: In section 2.1, the coupling between interconnects is analyzed. Section 2.2 shows the simple equations from a lumped RLC circuit. These equations help to achieve overshoot and undershoot expressions. Also, a comparison of the root loci for one, two, and three lumped stages is made in this section. Shielding strategies for reducing induced voltage noise are discussed in section 2.3. Section 2.4 shows some

aspects of signal quality. Ringing and undershoot values are characterized for different lengths of interconnects with open shield defects. Regions for acceptable and non-acceptable signal integrity levels are established in section 2.5. Finally, conclusions are given in section 2.6.

## 2.1 Coupling between interconnects

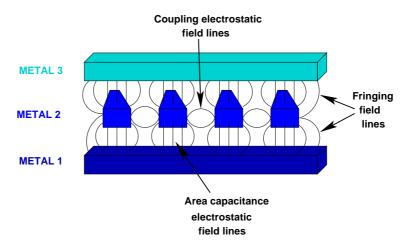

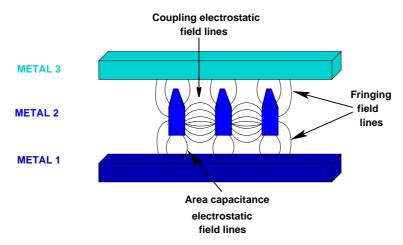

In deep-submicron technologies the on-chip wire density is very high. Current interconnect features allows to implement wires nearest to each others. Each wire is electrostatically coupled with its closest neighbors [52] [53]. Fig. 2.1 shows the coupling cases of on-chip wires. When scaling all dimensions, the capacitance per unit length among the wires remains unchanged. This is true if the wire thicknesses is also scaled. If the scaling factor is S, the resistance per unit length is increased by a factor of  $1/S^2$ . This means that the constant RC is increased due to dimension scaling [54] [55] [56] [57].

If the wires spacing is comparable with the metal thickness, the coupling

Figure 2.1: Coupling features of the alternated in direction metal interconnects. The physical localization and the shape of the interconnects generate the coupling, fringing and area capacitance

capacitance between wires has a considerable value [34]. Fig. 2.2 shows graphically this phenomenon. Because this, it is important to take into account the coupling capacitance between interconnects and its impact in the

signal integrity. Faster switching signals require interconnects with lower re-

Figure 2.2: The coupling capacitance between interconnects dominates the total interconnect capacitance.

sistivity in order to reduce the RC delay. Decreasing interconnect resistance is achieved using thicker, wider interconnects and also new materials. However, if the resistance of the interconnect is reduced, the currents increase and the inductance become an important factor in multi-coupled interconnects. In Buses with multi-coupled interconnects and long clock distributions, the inductance effects are evident and play an important role in the signal integrity quality [56] [23] [58] [59]. Many techniques have been developed in recent years in order to reduce inductive parasitic effects in high speed interconnects [43] [37] [36] [38].

Low frequency circuits could be modeled like resistive and capacitive devices, and the connection between two of them should be considered as a single node. This approach is no longer applicable in today's high performance circuits, where a good prediction of the behavior is required. High frequency operation at the limit of VLSI circuits cause interconnects to have greater impact on the overall system behavior. Because of the increment in frequency operation and circuit complexity, the wires should be modeled as distributed resistance, capacitance and inductance [56] [5].

Signal integrity is an important factor when determining the reliability and performance of electronic circuits, and many resources are therefore required

to obtain specific signal integrity levels [60] [19] [61] [62] [63]. Signal current variations in a transmission line generate a variable magnetic field. This flux creates induced voltage noise in nearby loops. Shielding techniques have been developed to reduce the mutual inductance of signal lines. This allows induced noise to be decreased [36]. The connections of shielding lines to ground may present resistive open defects [38]. A resistive open appears when the conductive material is not completely broken. Via-contacts are a likely place for opens to occur [64] [65] [66] [67] [68]. Random particle induced-contact defects are the main test target in production testing [67]. In copper-based technologies more defective connections are expected. The number of open defects is greater in copper than in aluminum [69]. These defects indirectly affect the integrity of signal traveling in adjacent signal lines. Ringing values of the signal may vary significantly. Hence, a faulty behavior of the system can occur.

In this chapter, we study the effect of resistive open defects in the grounded shielding line connection. We compare the dominant pole loci of the lumped RLC circuit with distributed RLC circuits in order to determine the region of signal integrity violation. Graphs of overshoot and undershoot values are shown for different interconnect lengths and resistive open defect values.

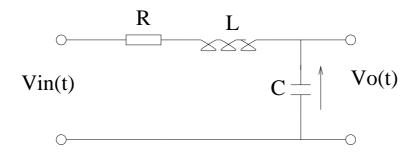

## 2.2 Simple interconnect models

The simplest equivalent circuit of a transmission line is a lumped RLC circuit which has a second order transfer function. Varying the inductance from zero to high values, we can plot the trajectory of the equation's roots and identify the over-damping, critical-damping, and under-damping regions. Proper modeling of parasitic interconnect components is required to evaluate the performance of high speed circuits [70] [71]. In [72], the authors model conductors using surface-only triangular meshes. Interactions between Rao-Wilton-Glisson basis functions are used to form a coupled matrix which also includes the modified nodal analysis (MNA) of circuits. This method for modeling interconnects is relatively complex. Furthermore, the use of ideal voltage sources neglects driver impedances and load. A method that generates a passive low order model from a large PEEC(Partial Element Equivalent Circuit)-like circuit models is presented in [60]. In [73] Chen et. al present a grid model to represent on-chip power bus structures. The meth-

ods mentioned above are complex and require large computation resources to predict interconnect behavior. Interconnects should be modeled in a number of ways, varying accuracy and computational overhead. Problems such as timing, power, noise and reliability can be included in the interconnect model [30].

In this work, we analyze interconnect representation including driver impedance and its equivalent load. The loci of the dominant poles for the equivalent circuit have been used to predict signal integrity violations in the presence of defects.

#### 2.2.1 One stage model

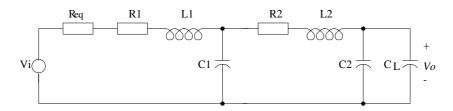

A transmission line can be modeled with a simple equivalent RLC circuit (Fig. 2.3).

Figure 2.3: Lumped RLC circuit of the interconnect

The characteristic equation considering the driver, line and load is:

$$L(C_i + C_L)\frac{d^2V_o(t)}{dt^2} + (R_i + R_{eq})C\frac{dV_o(t)}{dt} + V_o(t) = V_i(t)$$

(2.1)

and

$$R = R_i + R_{eq}$$

$$C = C_i + C_L$$

Where  $V_o(t)$  is the voltage developed at the capacitance C.  $R_i$  and  $C_i$  are the interconnect resistance and capacitance respectively,  $R_{eq}$  and  $C_L$  are the

Figure 2.4: Loci of poles of the lumped RLC model of the transmission line as inductance (L) increases

resistance of the interconnect driver and the input capacitance of the load buffer.

Applying the Laplace transform to equation 2.1

$$V_o(s)LCs^2 + V_o(s)RCs + V_o(s) = V_i(s).$$

(2.2)

The poles of the transfer function are the solutions of the characteristic equation [5]:.

$$s = \frac{-(RC) \pm \sqrt{(RC)^2 - 4(LC)}}{2LC}$$

(2.3)

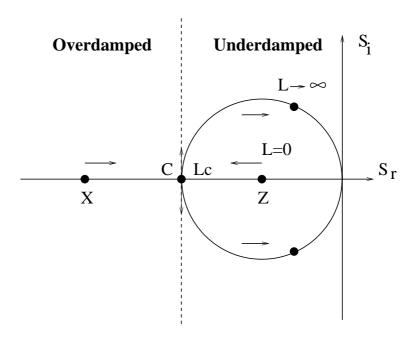

The track of s on a complex frequency plane when L is increased from a small value to larger values is shown in Fig 2.4. The trajectories start at X and Z for small L, and go through the critical damping point C at  $L = L_c$ . The critical damping point is obtained when  $L = \frac{R^2C}{4} = L_c$ . Here s is a pair of complex conjugate numbers in the under-damping region if  $L > L_c$ . At the point C and for  $L > L_c$ , the signals present ringings.

#### 2.2.2 Two stage model

A more accurate model of the interconnection is obtained with a two-stage RLC model, as indicated in Fig. 2.5.

Figure 2.5: Distributed two stage RLC circuit model for the transmission line

The characteristic equation of this system is given by [5]:

$$A4s^4 + A3s^3 + A2s^2 + A1s + 1 = 0 (2.4)$$

where:

$$A4 = (L1C1)(L2(C2 + C_L))$$

$$A3 = (L1C1)(R2C2) + (L2(C2 + C_L))((R_{eq} + R1)C1)$$

$$A2 = (L1C1) + (L1(C2 + C_L)) + (L2(C2 + C_L)) + (R2(C2 + C_L))((R_{eq} + R1)C1)$$

$$A1 = ((R_{eq} + R1)C1) + ((R_{eq} + R1)(C2 + C_L)) + (R2(C2 + C_L))$$

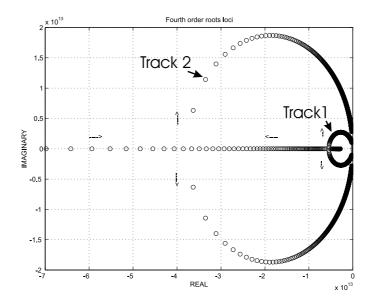

The trajectory of the poles of Eq.(2.4) is shown in Fig. 2.6.

Fig. 2.6 shows that two trajectories appear in this case (track 1 and 2). The trajectory with the dominant poles (track1) is the trajectory with the smallest real and imaginary parts.

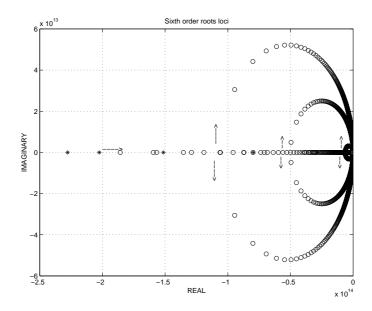

### 2.2.3 Three stage model

A model with three RLC stages corresponds to a sixth order system. It has three trajectories of roots where one pole trajectory is also dominant (track1), as Fig. 2.7 shows. If we have distributed transmission line models with more stages, for example four or five, the grade of the characteristic equation grows by a factor of 2\*N, where N is the number of stages employed to model the lumped circuit. Thus, we have four roots for a two-stage model, six roots for a three-stage model and so on. In all cases only one trajectory of dominant

Figure 2.6: Loci of poles of the two-stage distributed model as inductance (L) increases

Figure 2.7: Loci of poles of the three-stage distributive model as inductance (L) increases

poles exists, which has roots closer to the imaginary axis and lower frequency oscillation than the other trajectories. Hence, using the dominant poles is a good approximation of the pole trajectories of the second order system. Next, the second order system equation is analyzed in order to obtain an expression for overshoots and undershoots.

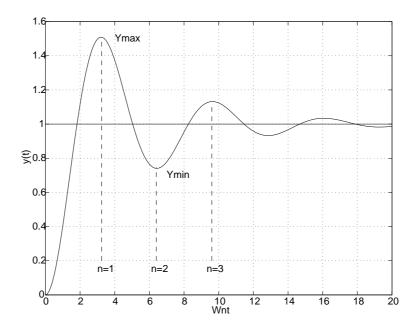

The equation of a second order system in the frequency domain is [39]:

$$Y(s) = \frac{w_n^2}{s(s^2 + 2\zeta w_n s + w_n^2)}$$

(2.5)

Where  $w_n$  is natural frequency of the system and  $\zeta$  is the damping factor. Applying a unit-step input function and taking the inverse Laplace transform of the equation of the result is:

$$y(t) = 1 - \frac{e^{\zeta w_n t}}{\sqrt{1 - \zeta^2}} \sin(w_n \sqrt{1 - \zeta^2} t + \cos^{-1} \zeta) \quad t \ge 0$$

(2.6)

The maximum overshoot can be obtained by taking the derivative of Eq. 2.6 with respect to t and setting the result equal to zero. Applying this, we obtain

$$t = \frac{n\pi}{w_n \sqrt{1 - \zeta^2}} \tag{2.7}$$

t indicates the time when the ringings of the signal have the maximum a minimum values. The overshoots occur at odd values of n, that is, n=1,3,5,... and the undershoots occur at even values of n. Fig. 2.8 plots y(t) for a  $\zeta = 0.2$ . It can be observed that the maxima and minima occur at periodic intervals.

The maximum overshoot and the minimum undershoot are obtained substituting eq. 2.7 into eq. 2.6 and setting n=1 and n=2, respectively.

$$maximum \ overshoot = y_{max} - 1 = e^{-\pi\zeta/\sqrt{1-\zeta^2}}$$

(2.8)

minimum undershoot =

$$1 - y_{min} = e^{-2\pi\zeta/\sqrt{1-\zeta^2}}$$

(2.9)

The poles with the same  $\zeta$  are located in straight lines on the s-plane passing through the origin and with slope  $\pm \frac{\sqrt{1-\zeta^2}}{\zeta}$ .  $\zeta$  is correlated with the interconnect parameters as  $\zeta = \sqrt{\frac{R^2C}{4L}}$ . Where R, L, and C are the resistance, inductance, and capacitance related with the interconnect respectively.

Figure 2.8: Transient response for the Second order system for a unit step signal. Maxima and minima of the response are indicated (n=1,2,3)

The dominant poles located in the lines have the same  $\zeta$  and consequently the same overshoot (undershoot). Later these lines will be used to determine the signal integrity regions on the s-plane (see Fig. 2.17). Table 2.1 shows pole values for the lumped and the distributed models of interconnects. Hspice internal field-solver tool has been used in order to obtain the interconnect parameters. Using the extracted parameters, electrical simulation were made to obtain the dominant poles. In our case, the dominant poles have the minimum real and imaginary values. Hence, if only a pair of poles has important information, they correspond to a Second order system. The values of the overshoot and undershoot can be estimated with this approximation.

# 2.3 Shielding practice

Shielding lines are used to reduce the coupling inductance effect of a transmission line [15] [36] [74]. Shielding lines are grounded to the substrate, and

| Model  | Simulation Pole Value       | ζ     |

|--------|-----------------------------|-------|

| lumped | $-1.1446E+10\pm2.3441E+10i$ | 0.438 |

| dist2  | $-1.2449E+10\pm2.7623E+10i$ | 0.41  |

| dist3  | $-1.2525E+10\pm2.9212E+10i$ | 0.394 |

| dist4  | $-1.2725E+10\pm3.0035E+10i$ | 0.390 |

| hspice | $-1.3329E+10\pm3.3137E+10i$ | 0.373 |

Table 2.1: Pole values for 1, 2, 3, 4, and 20 stage model having dominant poles in all cases

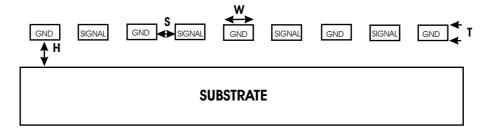

placed between signal lines in order to reduce mutual inductance between signal lines. When the shielding lines are inserted between two critical lines, almost all capacitive coupling noise between the two lines are eliminated. The shielding lines also help to reduce the self-inductance effects of a line by generating a current return path very close to the signal line [75] [76]. This also reduce the inductive coupling between lines of either side of the shield. Several kind of conductive shielding lines could be implemented like shields connected to VDD or GND or active shields [37] [77] [78]. In this work, the case of the shield connected to GND is analyzed. Fig 2.9 shows the interconnect system structure used for simulation analysis. The dimensions H, S, W and T represent the height, separation, width and thickness of the interconnect, respectively. Each signal line is located between two shielding lines

Figure 2.9: Bus system with shielding lines

in order to reduce crosstalk noise. This shielding technique has high area overhead. However, it is widely used for high speed signal systems with long interconnects [36] [34].

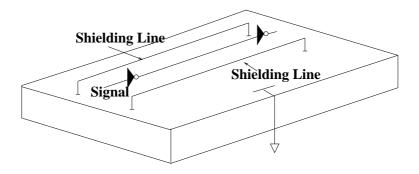

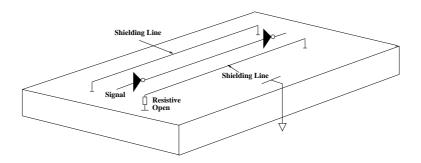

Shielding lines are grounded to the substrate at each end of the line. Open defects in one ground connection in the shielding line may produce a degra-

dation of the shielding function. Fig. 2.10 and 2.11 show the faulty-free shielding line connection and faulty shielding line connection, respectively. If an open exists, it could be modeled as resistive open (Fig 2.11) with

Figure 2.10: Grounding the shielding line at both ends of the shield.

Figure 2.11: Faulty shielding due to a resistive open in the grounding connection.

different resistance values. Realistic resistive opens have values from some tens of ohms to some hundred kilo ohms[64]. In this experiment we take into account resistive opens from  $100\Omega$  to  $150~K\Omega$ . Above  $150~K\Omega$  (even for full open defects) the behavior is similar to  $150~K\Omega$ . Fig. 2.12 shows the case for a resistive open in one ground connection.

In the next section we analyze the signal integrity of signal behavior when a defect (resistive open) occurs in the shield ground connection.

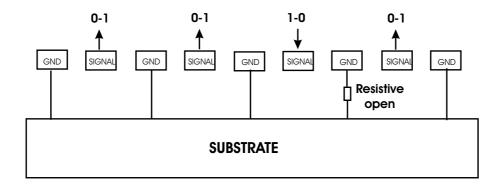

Figure 2.12: Faulty ground connection in one shielding line having a resistive open with the worst case excitations.

# 2.4 Characterization of signal quality

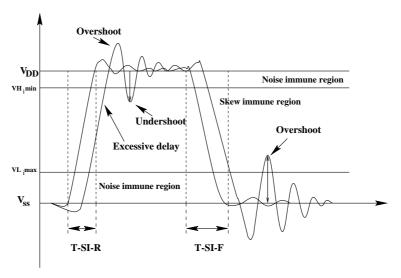

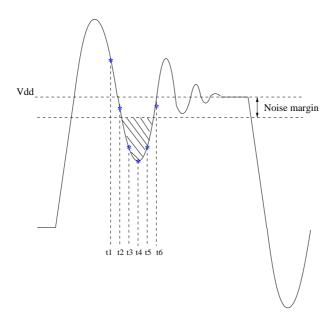

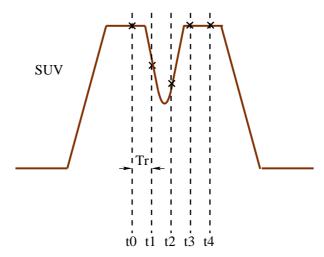

In general, integrity of a signal indicates its compliance of the static and dynamic logic signal specification [46] [79] [80]. In practice, logic circuits can tolerate some levels of noise. For example, a CMOS gate interprets as logic 1 input voltages in the  $[V_{H_imin}, V_{DD}]$  range and any voltages in the  $[V_{ss}, V_{L_imax}]$  range as a logic 0 (See Fig 2.13). Electronic circuits allow some amount of delay skew i.e. T - SI - R and T - SI - F for rising and falling delays. In this work the minimum undershoot and the maximum overshoot (Fig 2.13) on shielded bus lines are investigated. Undershoots and overshoots that are outside of the immune region produce a signal integrity violation. For example, a signal integrity violation occurs if the overshoot is bigger than  $V_{L_imax}$  voltage level as indicated by 2.10:

$$\frac{Overshoot}{V_{L_imax}} > 1 \tag{2.10}$$

We have considered four signal lines switching simultaneously, one of them in the other direction of the others (See Fig. 2.12). Each one is located between two shielding lines. One of the shielding lines has a resistive open defect in one side. The effect on the signal traveling next to the defective shielding line is studied. Resistive opens with values of 100 200, 300, 500, 1K, 10K, 100k and 150K ohms are used for interconnect lengths of 1, 2, 3, 4, and 5 mm and three different drivers. The aspect ratio of the nominal driver is modified  $\pm 50\%$ . We use 100nm MOS technology for Hspice simulation with a  $V_{tn}=260mV$ ,  $V_{tp}=-303mV$  and  $V_{DD}=2.5$  [81].

$VL_i max/VH min$ : Maximum/Minimum input voltage guaranteed to be recognized as 0/1

T-SI-R/ T-SI-F : Skew immune range (rising/falling)

Figure 2.13: Integrity loss due to undershoot and overshoot in long interconnect lines.

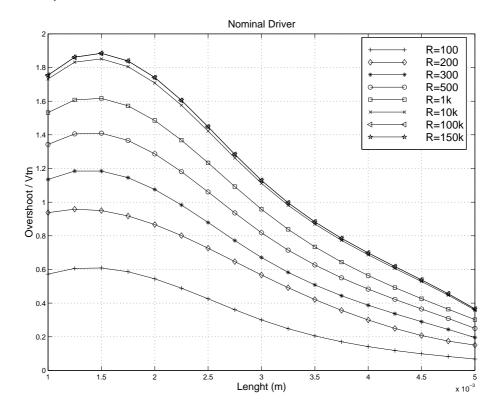

Fig 2.14 shows the overshoot versus interconnect length using the nominal driver. The value of overshoot is normalized to Vtn. For lines below 2.3mm and resistive opens above  $300\Omega$  may show signal integrity violation (SIV) with  $\frac{Overshoot}{V_{L_imax}} > 1$ . Resistive opens of  $1K\Omega$  could produce SIV in lines

Figure 2.14: Overshoot Vs Length of the interconnect with a defective (resistive open) shield. R values from  $200\Omega$  to  $150~k\Omega$  and Length values from 1mm to 5mm with a nominal driver

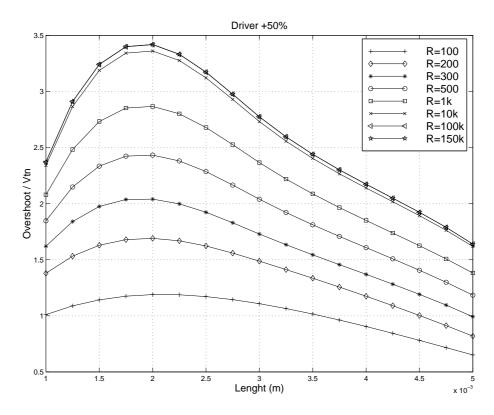

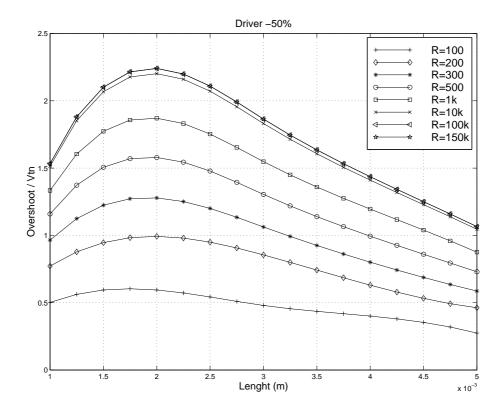

shorter than 2.9mm. For full open  $(R=\infty)$  defects on the shield the SIV may appear in lines shorter than 3.3mm. Increasing 50% the size (channel width) of the nominal driver, the SIV in lines shorter than 3.6mm become visible for resistive opens with  $100\Omega$  (See Fig. 2.15). Resistive opens above  $300\Omega$  may cause SIV for lines below 5mm. Fig. 2.16 shows the overshoot versus interconnect length where the nominal driver is decreased 50% in size. In this case, a resistive open defect on the shield of  $300\Omega$  produces SIV in lines below 3.3mm. Lines shorter than 4.6mm may have signal integrity problems if a resistive open defect on the shield occurs with values above  $1k\Omega$ .

Figure 2.15: Overshoot Vs Length of the interconnect with a defective (resistive open) shield. R values from  $200\Omega$  to  $150~k\Omega$  and Length values from 1mm to 5mm with 50% higher driver than nominal driver.

Figure 2.16: Overshoot Vs Length of the interconnect with a defective (resistive open) shield. R values from  $200\Omega$  to  $150~k\Omega$  and Length values from 1mm to 5mm with a 50% smaller driver than nominal driver.

## 2.5 S-Plane signal integrity regions

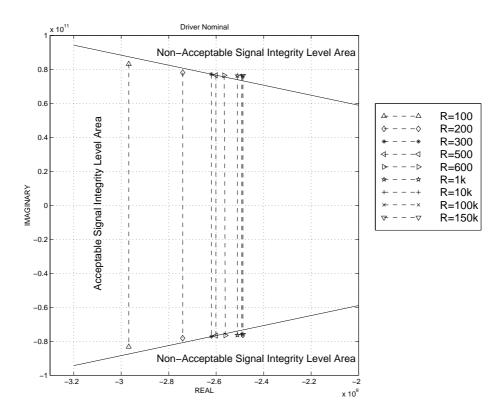

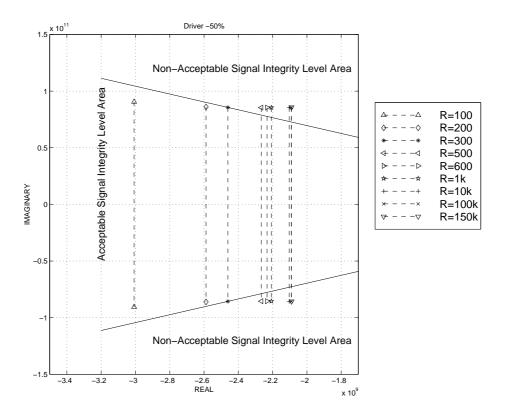

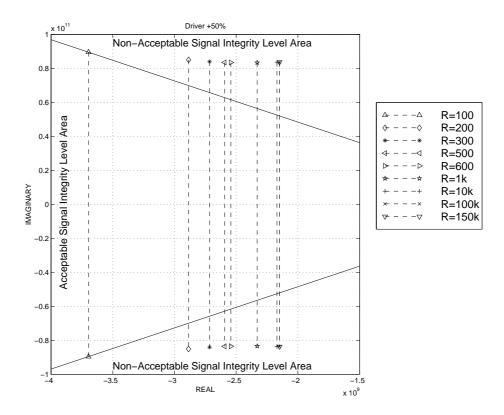

As shown in the previous study using electrical simulations, a defective shield connection may change the signal integrity quality. Resistive open defects of a shielding line affect the shielding function. Because of this, the characteristics (RLC) of the signal lines next to it are modified. The dominant poles can be plotted in order to establish its loci in the S-plane. The poles in Figs. 2.17, 2.18, and 2.19 are the dominant poles, they were extracted from the output waveform obtained by Hspice simulation on the bus system showed in Fig. 2.12. The three different aspect ratios of the driver are used. The two areas for acceptable and non-acceptable signal integrity regions are indicated in Fig. 2.17 for a nominal driver. Figs. 2.18 and 2.19 show the same areas, but with a decreased and increased driver size, respectively. Pole loci allows to determine if the resistive open produce or not a signal integrity violation. For a resistive open value of  $300\Omega$ , the level of ringing become higher than  $V_{tn}$  using the nominal driver and the decreased driver size. If the increased driver sized is used, the ringing could be higher than  $V_{tn}$  for resistive open defects above  $100\Omega$ . Increasing the value of the resistive open results in a change of the waveform shape. Hence, there is a change in the pole loci as Figs. 2.17, 2.18, and 2.19 show.

#### 2.6 Conclusions

The signal integrity in shielded transmission bus lines has been studied and characterized by electrical simulation. Shielding lines help to decrease inductance and capacitance coupling in long interconnects. These lines are grounded to the substrate by vias. If a resistive open occurs in this ground connection the impact on signal interconnects may produce signal integrity violations. It has been found that in presence of resistive open defects on shielding lines, the neighboring signals could fall out of the noise immune regions. Hence, this may produce a faulty behavior of the next gate or block that is driven by the affected interconnect.

The trajectory of the roots of the characteristic equation shows the interconnects behavior when the inductance varies. The inductance changes with interconnect geometry. For thicker and wider interconnects, the resistance per unit length is reduced significantly, hence the inductance effects become 2.6. Conclusions 35

Figure 2.17: Pole loci for different resistive opens on the shield for a bus interconnect of length l=2mm and using nominal driver.

36 2.6. Conclusions

Figure 2.18: Pole loci for different resistive open on the shield for a bus interconnect of length l=2mm and using decreased driver.

2.6. Conclusions 37

Figure 2.19: Pole loci for different resistive open on the shield for a bus interconnect of length l=2mm and using increased driver.

38 2.6. Conclusions

important. Also, using new low resistive metals helps to increase the inductance effects.

The property of the trajectory roots can be used to identify if the interconnect has an underdamping or overdamping deportment. It is shown that for an N-stage model we have N trajectories for the poles but only one is dominant. Thus a pair of dominant poles is sufficient for signal integrity analysis. The signal integrity level taken in this work was established for 100nm technological parameters and the measurement values of overshoots was normalized with respect to  $V_{th_n}$ .

Acceptable and non-acceptable signal integrity regions were established with the pole loci. A line placed from 0 and crossing the first complex pair of pole that cause signal integrity violation helps to determine the area for signal integrity violations. The overshoot is analyzed for different resistive open values in the grounded shield connection and for three different sizes of driver. It is shown that for resistive opens with  $1K\Omega$  and using nominal driver could produce SIV in shorter lines than 2.9mm. For full open  $(R = \infty)$ defects on the shield the SIV may appear in shorter bus lines than 3.3mm. Increasing by 50% the size of the nominal driver affects the transmission line behavior. The SIV in lines below 3.6mm become visible for resistive open defects with  $100\Omega$ . Resistive open defects with values above  $300\Omega$  may cause SIV for lines below 5mm. When the nominal driver is decreased 50% in size, resistive open defect on the shield with  $300\Omega$  could cause SIV in lines below 3.3mm. Shorter lines than 4.6mm may have signal integrity problems if a resistive open defect on the shield occurs with values above  $1k\Omega$ . The size of the driver, together with resistive open defects, have an important impact on pole loci. Hence, the behavior of the transmission line is changed.

# Chapter 3

# Verification of signal integrity using High Speed Monitors

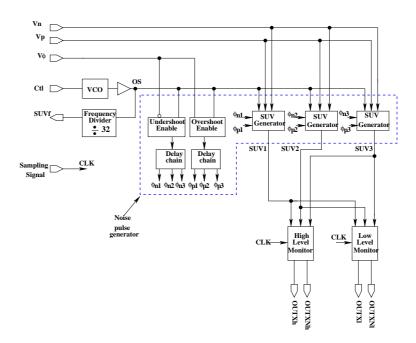

Signal integrity verification is becoming an important issue as technological process features continues to shrink and logic speed increases. Advanced technologies permit to integrate a large number of devices onto a chip. Current high performance systems require to assure good levels of signal integrity. In this chapter a signal integrity verification methodology is presented. The chapter presents an introduction of the signal integrity as a problem in current high performance integrated circuits. Next a methodology to verify the signal integrity is proposed. Sensors to monitor the signal integrity are proposed. The resulting cost for implementing this signal integrity methodology is evaluated. Next, the sampling technique used in this proposal is described. The strategy to generate the control and enable signals for the monitors and the possible measurement errors of the proposed methodology, are also explained in this chapter.

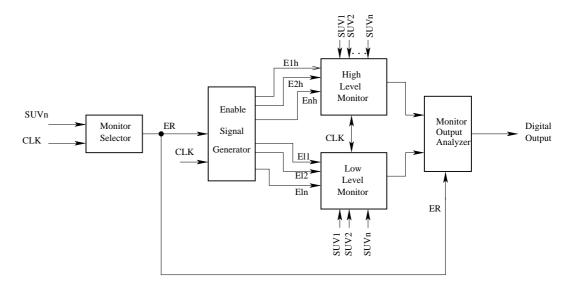

The rest of the chapter is organized as follows: In section 3.1 an introduction for signal integrity issues in current technologies is presented. A methodology for signal integrity verification is proposed in section 3.2. Next, the proposed sensors to monitor the signal integrity violation are presented in section 3.3. Section 3.4 presents the coherent sampling technique used for the proposed methodology. The monitoring system architecture is presented in section 3.5. In section 3.6 and 3.7 the accuracy and cost of the proposed methodology is evaluated. Finally the conclusions of the chapter are given in section 3.8.

40 3.1. Introduction

#### 3.1 Introduction

While nanometric technologies enable to integrate circuits (ICs) with more functionality, transistors per  $\mu m^2$ , interconnect density, etc. [14] [82] [83], the designer needs to prevent problems as crosstalk noise, substrate noise, power supply voltage drop, etc. [9] [5] [57] [8]. All these factors can affect the SI and may produce an unreliable performance of the system. Preserving signal integrity (SI) in complex designs is a current challenge in nanometric technologies [20] [84] [85].

Signal integrity could be defined as the ability of a signal to generate assured correct responses in a circuit. A signal with good SI has digital levels with required voltages levels at required times [7]. For designers good levels of SI means clean data, free of ringings, and not sensitive to interferences. However, high performance systems, for example SoCs (Fig. 3.1), made in nanometric technologies, lead to have signals with unavoidable noise levels. Digital and analog cores can share the same substrate, the noise generated by the digital core could affect the performance of analog core. The large amount of interconnects in current integrated circuits, carrying out high speed signals, interact between them by the action of parasitic elements producing signal integrity degradation [86] [87] [88].

Digital and mixed-signal circuits can be affected by internal switching noise [89] [90]. Internal noise, for example interference noise, is caused by internal transient currents flowing through the package parasitics. These currents are generated by the synchronized switching activity of the millions of the digital gates of the chip. These injected currents, substrate noise and voltage fluctuations of the power/ground lines could affect the performance of the digital and sensitive analog/mixed signal circuits [91] [92] [93]. Other source of internal noise is the electromagnetic environment in which the electronic systems have to work. The electromagnetic phenomenon is caused by the high rates of the switching activity of the signals traveling on the interconnects [94]. External noise could be generated by the radiation of the chip to chip interconnects that behaves like antennas. Current spikes generated by the high speed signals can affect the performance of the components mounted on the same board [14] [22] [95]. In general, integrity of a signal indicates its compliance of the static and dynamic logic signal specification [96] [46].

Figure 3.1: SoC structure example: Several analog and digital blocks work together

In practice, logic circuits can tolerate some noise levels. For example, a CMOS gate interprets as logic 1 or 0 if the input voltages are inside of the permitted noise margin region as Fig. 3.2 shows [46]. However, voltage levels in the middle region (see Fig. 3.2) may not be interpreted correctly by the next stage.

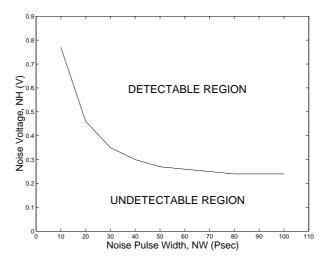

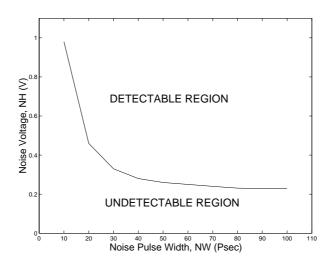

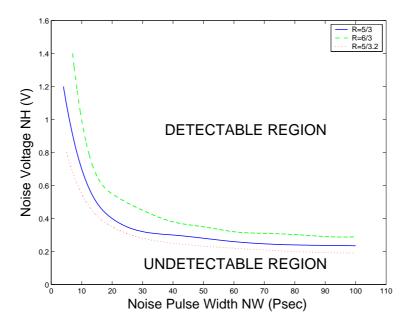

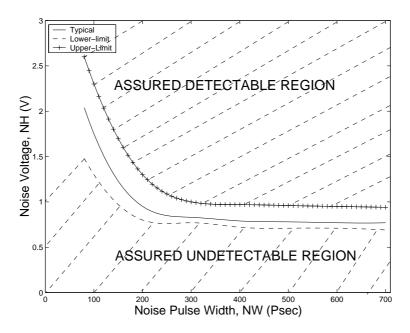

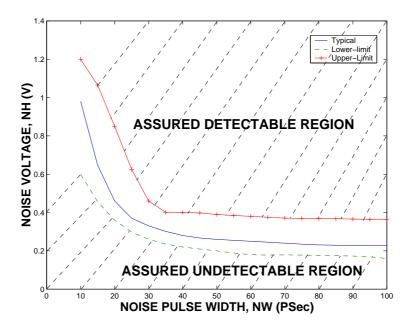

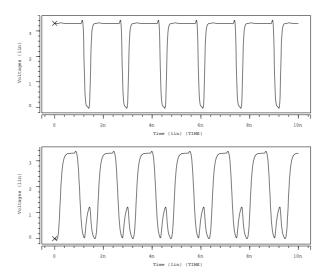

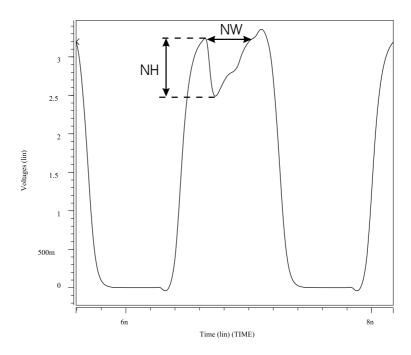

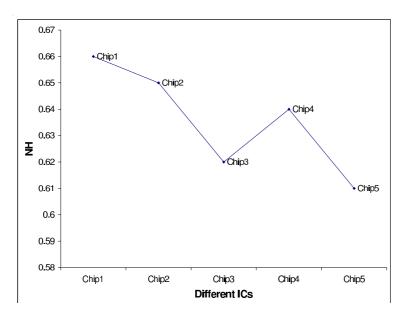

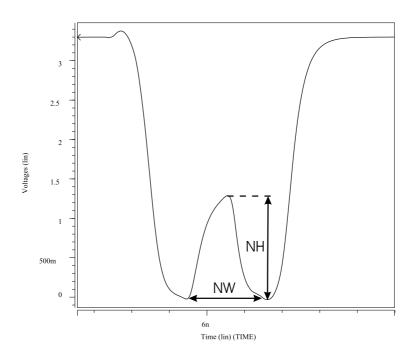

The voltage magnitude (NH) and the duration (NW) of the noise pulse over the signal determine the performance of the circuit receiving that noisy signal. NH is the voltage quantity that a high (low) logic level drops (rise) from VDD (GND). NW is the duration time of the noise pulse.

In the next section the proposed signal integrity verification methodology is presented.

# 3.2 Proposed Verification Methodology

Signal Integrity violation (SIV) occurs when the signal digital levels do not have the required voltages to achieve the correct performance. Signal ringings with forbidden voltage values are examples of SIV. Detecting (SIV) and

Figure 3.2: Signal having undershoot and overshoot outside of noise immune region. NH and NW are the voltage noise magnitude and the noise width respectively.

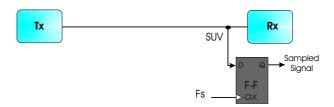

evaluating the obtained results by the monitors require an efficient methodology to ensure that all SIVs are being captured and processed without loss of information. Assuming that proper periodic input signals are applied to the block A (See Fig. 3.3), the signals arriving to the block B have a periodical behavior and some, or all of them, could be under verification. The block A could be any circuitry that generates periodic signals and the block B could be any circuitry that receives the signals generated by block A. These blocks are connected by on-chip metal lines. In this block diagram the block A and B are connected by long metal lines (interconnects in the range of millimeters) which may be affected by several sources of noise (capacitive and inductive coupling, reflections, radiations, etc.) .

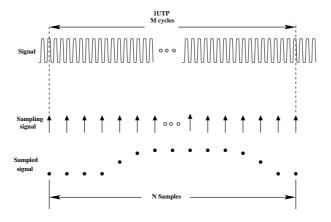

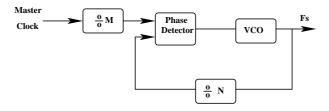

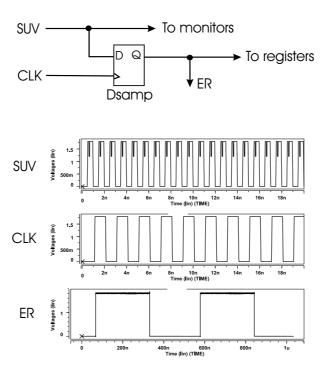

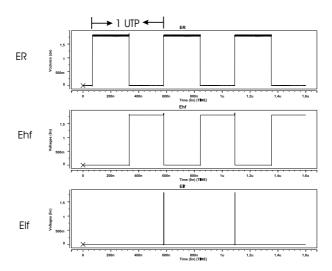

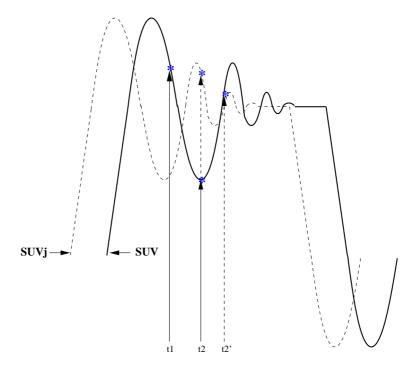

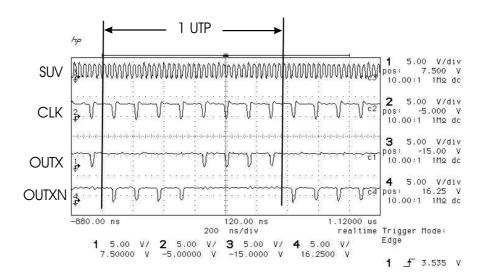

Two monitors (sensors in Fig. 3.3) are required for detecting the SIV, one of them is for monitoring SIVs at the high level (undershoots) and the other one is for monitoring SIVs at the low level (overshoots). The monitors are physically placed near to the block B or in a general way, near to the point where the sample of the signal under verification (SUV) is taken. Each monitor receives three signals at the time of test: a) the first one is the SUV from a point near to the block B, b) the second one is the sampling signal which has a coherent frequency [97] [98], and c) the third one is an enable signal. The coherent sampling generator block receives at its input the system master clock and by internal circuitry the clock signal is processed in order to obtain the required coherent frequency. The sampling signal generated by this block requires special features to obtain the effective sampling frequency for getting the overall information of the SUV [97][99].

The verification methodology uses an undersampling technique, called coherent sampling [97] [100]. Coherent sampling takes samples with high precision with relatively low sampling frequency. This allows to analyze the output of the monitors at low frequency rates and relaxing the design effort of the overall verification blocks. More details about how the coherent sampling frequency is generated will be given later. The enable signal is generated by the "enable generator" which takes samples of the SUV at the rate of the sampling frequency. Using both signals the circuitry inside of the block generates the signal EM, this signal enable either the high or low level sensor. Also this block generates the enable signal ER, where ER activates the corresponding registers for storing the output of the high or low level sensors. The monitor output analyzer receives and stores the high and low level

monitor output. This information is sent outside of the chip by an external pin to inspect externally the monitor outputs. Each one of the blocks will be explained later in more detail.

Figure 3.3: Block diagram of the general verification methodology.

# 3.3 Proposed sensors

Detection of signal integrity violations (SIVs) is the goal of our methodology. To carry out this, monitors able to sense these violations of integrity (undershoots, overshoots) are needed. Two monitors are proposed for sensing SIVs, specifically when undershoots and overshoots occur in a signal (See Fig. 3.2). High level SIV monitor senses integrity violation when a digital signal has ringings in the high logic level. If ringings are below of the threshold voltage of a gate that receives this signal, it could be interpreted erroneously as low logic level. In another hand low level SIV monitor sense integrity violation

when a digital signal has ringings in the low logic level.

Next subsections explain the behavior of the proposed high and low level monitors. High and low level monitors able to verify more than two signals are also presented. In the last subsection monitor performance has been characterized by function of noise width (NW) and noise height (NH).

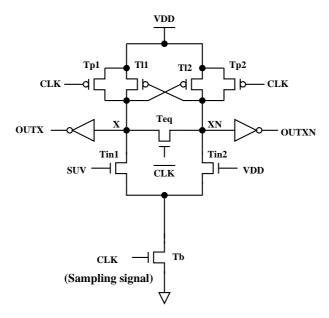

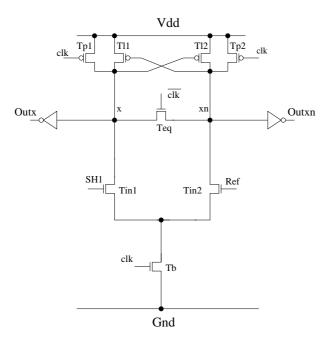

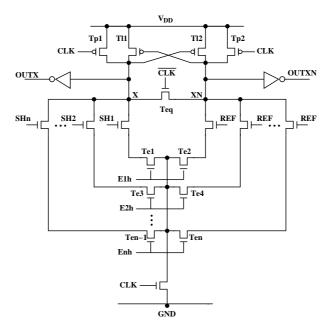

#### 3.3.1 High level SIV Monitor

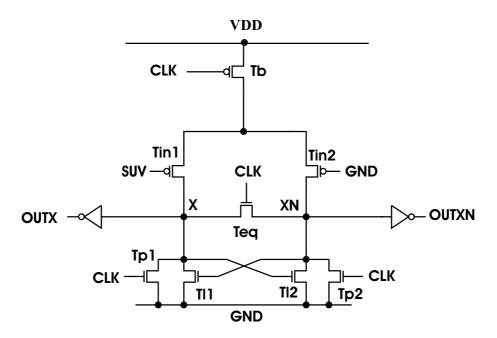

High level SIV Monitor consists of a differential pair with a latch as load (See Fig. 3.4). This architecture is similar to that proposed for the Mixed signal monitor [47]. The latch acts as load of the monitor. This latch is built with two cross-coupled PMOS transistors. It helps to switch the nodes X and XN to complementary logic levels. The load on the nodes X and XN and the size of  $T_{in1}$  and  $T_{in2}$  determine the speed of switching. Precharge transistors Tp1 and Tp2 must be designed to minimize load at nodes X and XN.

The methodology used to verify the SUV is as follows. The verification is

Figure 3.4: High level signal integrity violation monitor.

made in two steps, in the first step a pre-charge operation takes place by

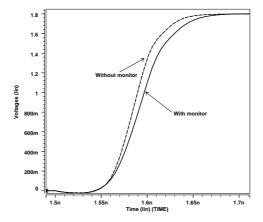

transistors  $T_{p1}$  and  $T_{p2}$ , when CLK is low, transistor  $T_{eq}$  helps to equalize nodes X and XN to  $V_{DD}$ . Transistor  $T_b$  is off, therefore no current path to GND exists through  $T_b$ . In the second step CLK is high and the transistors  $T_{p1}$ ,  $T_{p2}$  and  $T_{eq}$  are off. One input transistor  $(T_{in1})$  receives the signal under verification (SUV) and the other one  $(T_{in2})$  has a reference voltage as input that in this case is  $V_{DD}$ . The aspect ratio (W/L) of  $T_{in1}$  is larger than  $T_{in2}$  such that if the SUV is equal to  $V_{DD}$  the node X is discharged to GND by  $T_{in1}$  and  $T_b$ . The different aspect ratios establish a threshold detection voltage of the monitor.

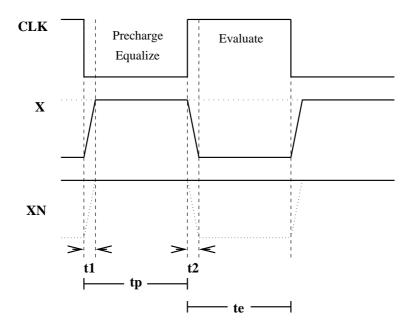

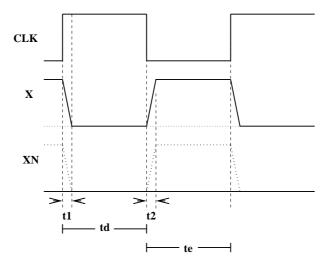

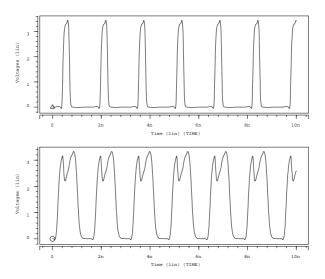

If the SUV has a value below of the threshold detection voltage, the node X remains to  $V_{DD}$  while the node XN is discharged to GND therefore a SIV is detected. This switching action is helped by the latch formed by the transistors  $T_{l1}$  and  $T_{l2}$ . Timing curves showing the behavior of the nodes X and XN are shown in Fig. 3.5. Time t1 is the time required for the monitor to have the precharge voltage levels. Time t2 is the time required to begin the evaluation of the SUV. Tp is the duration of the precharge stage and it must be longer than t1. The time te is the duration of the evaluate stage and it must be longer than t2.

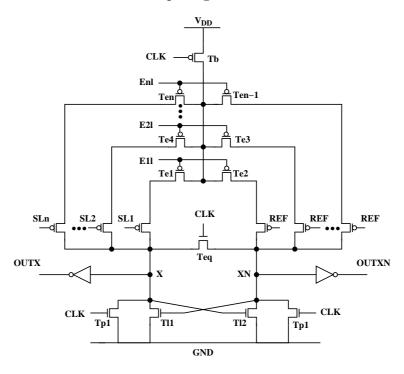

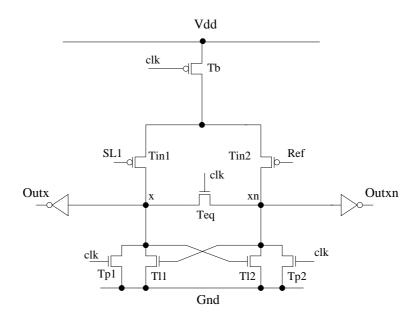

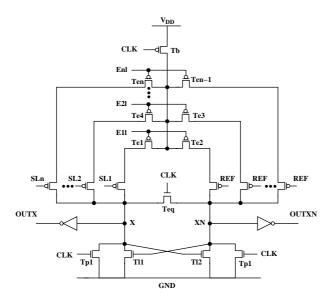

#### 3.3.2 Low level SIV Monitor

Low level SIV Monitor is a PMOS-Input differential pair with a latch made with NMOS transistors as Fig. 3.6 shows. The behavior is complementary to the high level SIV monitor. In this case, ringings that occur in a low logic level can be detected by the low level SIV monitor.

When CLK is high the nodes X and XN are discharged to GND by transistors  $T_{p1}$ ,  $T_{p2}$ , transistor  $T_{eq}$  equalizes nodes X and XN to GND. The sensing action of the monitor begins when CLK is low. The reference voltage in this case is GND. The aspect ratio between transistor  $T_{in1}$  and  $T_{in2}$  are different in order to have a threshold detection voltage. If the input signal (SUV) is a 0 logic level or below the threshold detection voltage, the node X will be charged toward  $V_{DD}$  by the action of transistors  $T_b$ ,  $T_{in1}$  and those in the latch formed by  $T_{l1}$  and  $T_{l2}$ . If the input signal is above the threshold voltage detection (an integrity violation) the node XN will be

Figure 3.5: Behavior of the signals at nodes X and XN under verification mode. Continuous line no SIV, dotted line SIV.

Figure 3.6: Low level signal integrity violation monitor.

charged toward  $V_{DD}$  by  $T_b$  and  $T_{in2}$ . The latch speed-up the switching action.

As explained above, the monitor behavior consists in precharge the nodes X and XN to GND (precharge phase) and evaluating the SUV with a reference voltage (evaluating phase). The ideal behavior of X and XN at these two phases is shown in the timing curves depicted in Fig. 3.7. tp is the time required for the precharging phase and te is the time needed for the evaluating phase.

Figure 3.7: X and XN behavior in one CLK period. Continuous line no SIV, dotted line SIV.

#### 3.3.3 Multi-signal Monitors

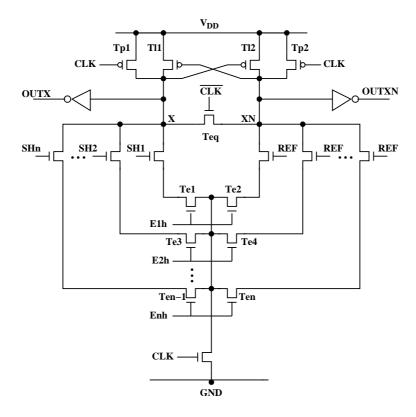

The monitors mentioned above have been adapted in order to sense multiple signals. The schematic of the modified monitors for the high and low level signal integrity monitors are shown in Figs. 3.8 and 3.9.

Adding equal n number of transistors in both input sides of the monitor (input an reference signals) and pair of enable transistors (signals  $E_n$ ), where n is the number of signals under verification, is possible to verify several signals. One signal is verified at a time enabling the control signal  $E_n$  that corresponds to the signal under verification. Equal number of input transistors and reference transistors are required for having the same load in the

Figure 3.8: High level signal integrity violation monitor with multi-input signals.

nodes X and XN. In a similar way, the low level signal integrity monitor has been modified to sense multiple signals.

Figure 3.9: Low level signal integrity violation monitor with multi-input signals.

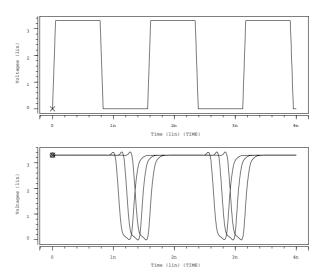

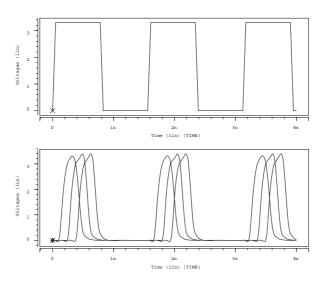

#### 3.3.4 Monitor Performance

The performance of the high (low) level monitor is characterized by the width, NW, and height, NH, of the signal going below (above)  $V_{DD}$  (GND) (See Fig. 3.2). Well defined rectangular shapes for the undershoots and overshoots have been considered. It has been considered a monitor with only one input signal to verify. The monitor design effort has been focus on detecting the noise pulse with the minimal duration. Monitor transistor are sized in order to obtain this goal. The transistor channel widths are indicated in Table 3.1. All of the channel length are the minimum allowed by the technology (180nm).

| Transistors | High level monitor $(\mu m)$ | Low level monitor $(\mu m)$ |

|-------------|------------------------------|-----------------------------|

| Tl1,Tl2     | 15                           | 3                           |

| Tp1, Tp2    | 2                            | 3                           |

| Teq         | 10                           | 10                          |

| Tin1        | 5                            | 8                           |

| Tin2        | 3                            | 3                           |

| Ten         | 4                            | 8                           |

| Tb          | 10                           | 15                          |

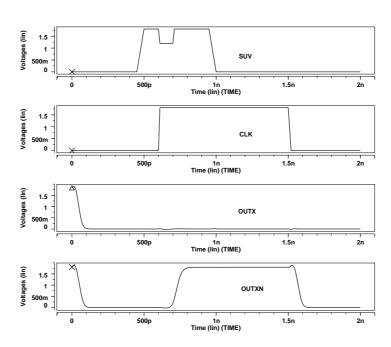

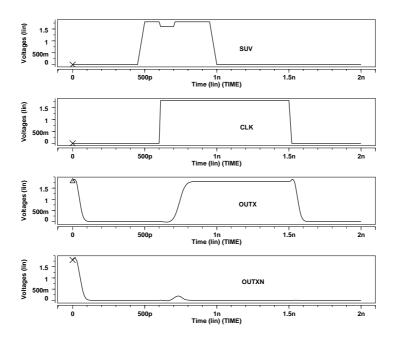

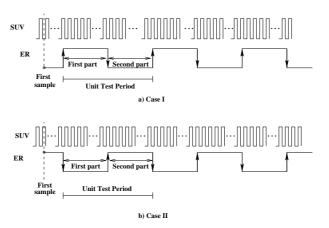

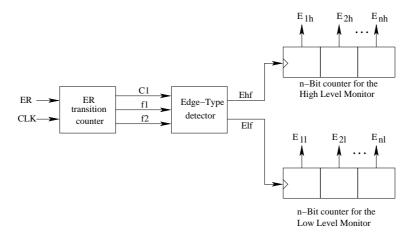

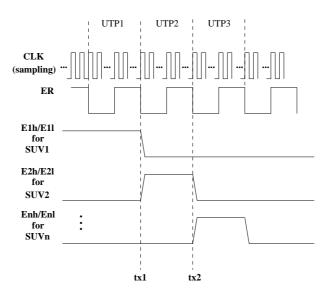

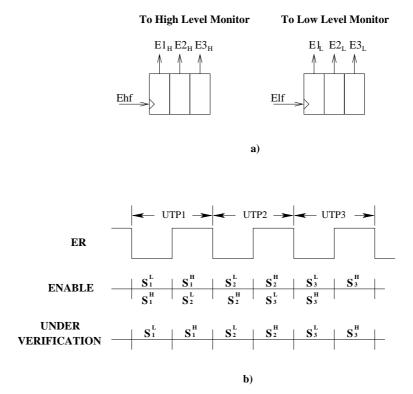

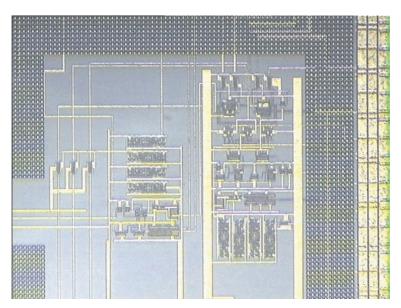

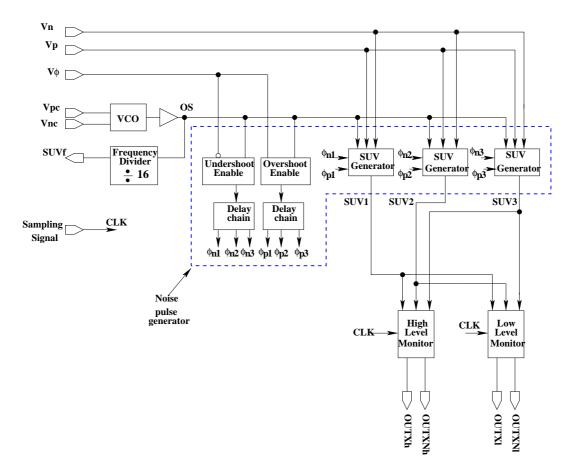

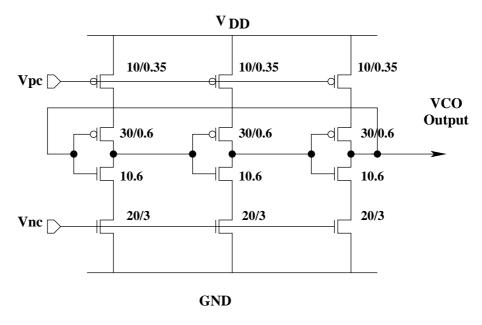

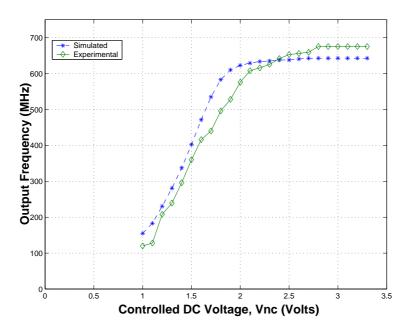

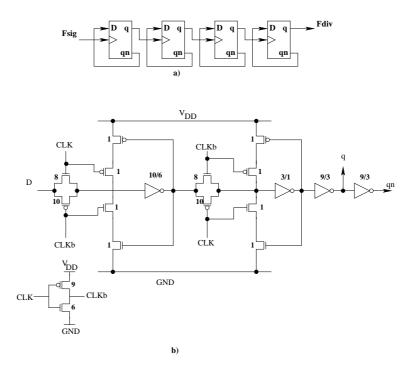

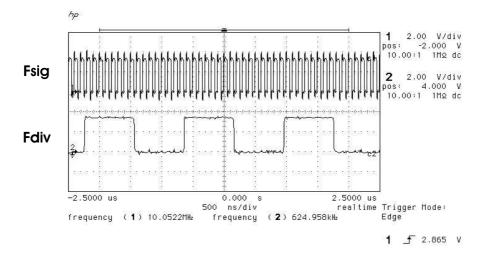

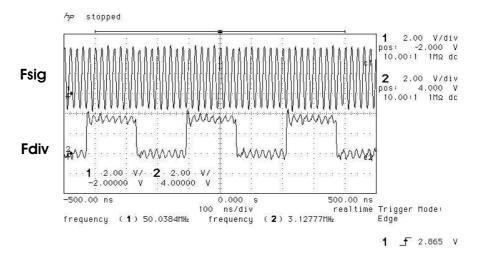

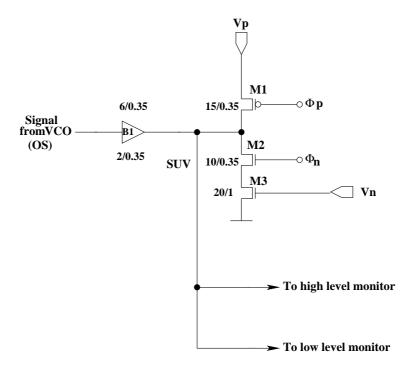

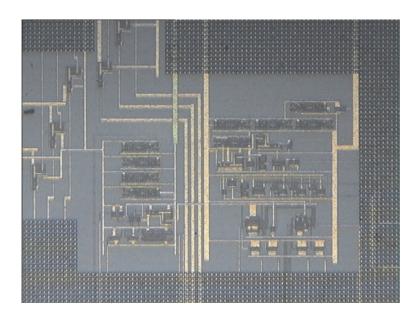

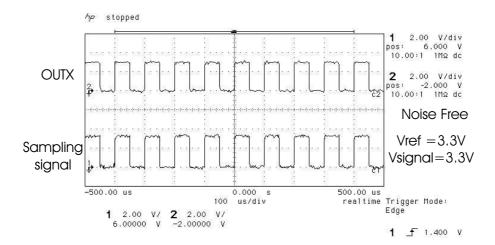

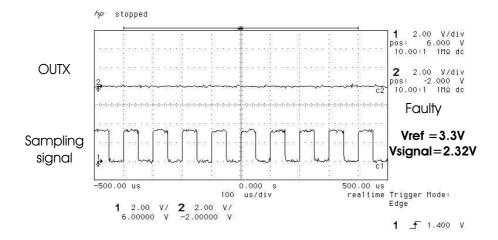

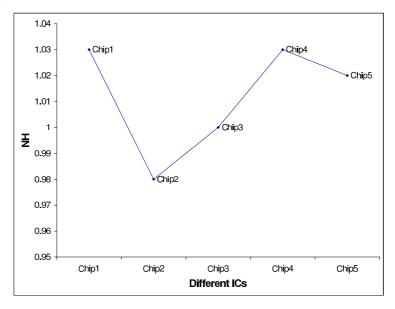

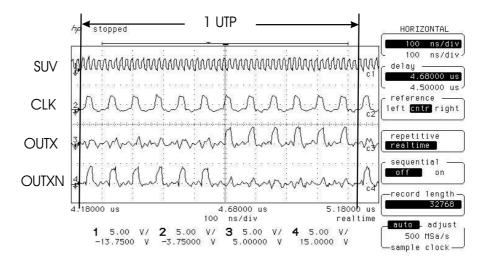

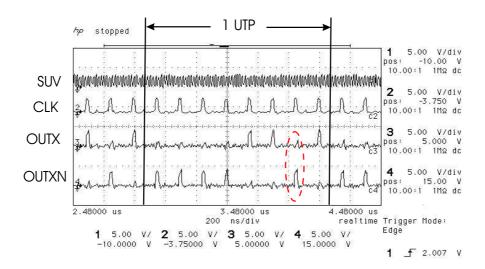

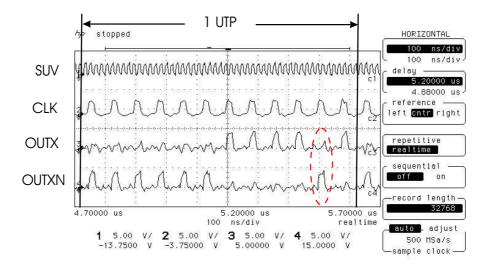

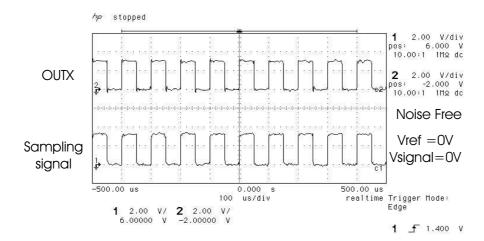

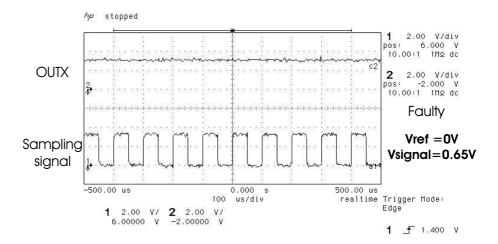

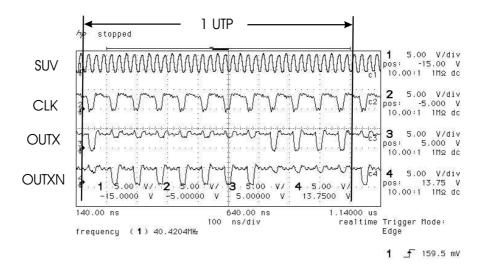

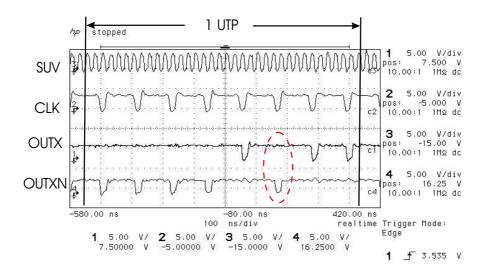

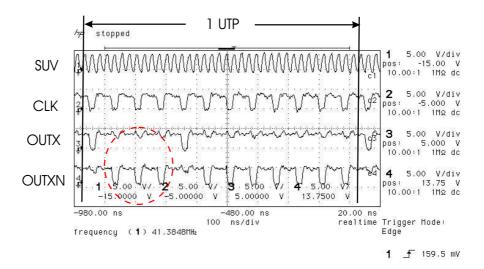

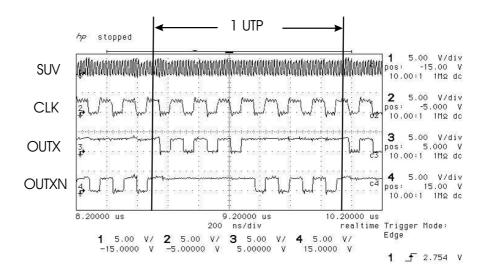

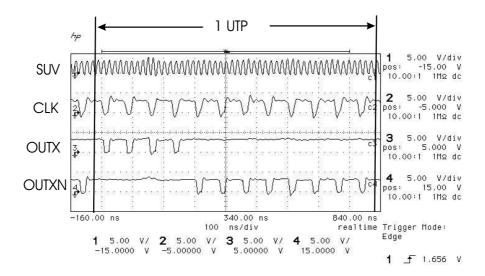

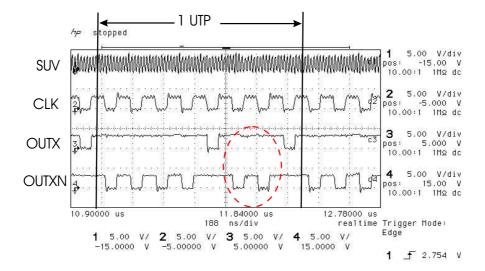

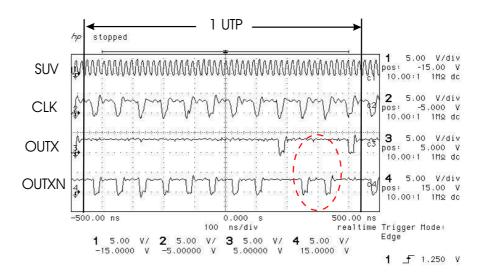

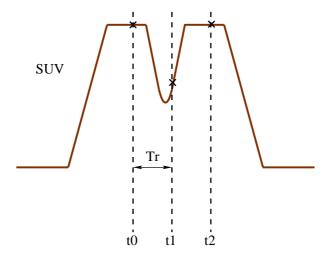

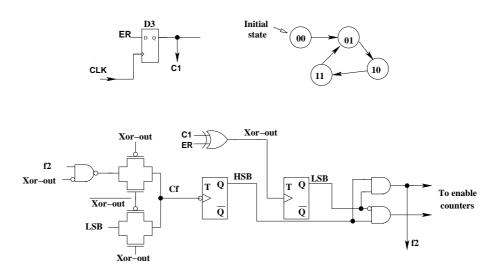

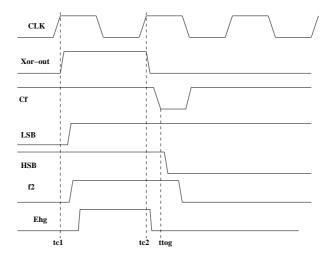

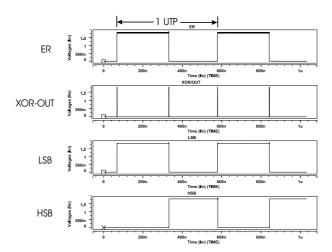

Table 3.1: Widths of the monitor transistors